Epson Research and Development

Page 13

Vancouver Design Center

Interfacing to the Toshiba MIPS TX3912 Processor S1D13505

Issue Date: 01/02/05 X23A-G-010-04

4.3 Memory Mapping and Aliasing

The TX3912 uses a portion of the PC Card Attribute and IO space to access the S1D13505.

The S1D13505 responds to both PC Card Attribute and IO bus accesses, thus freeing the

programmer from having to set the TX3912 Memory Configuration Register 3 bit

CARD1IOEN (or CARD2IOEN if slot 2 is used). As a result, the TX3912 sees the

S1D13505 on its PC Card slot as described in the table below.

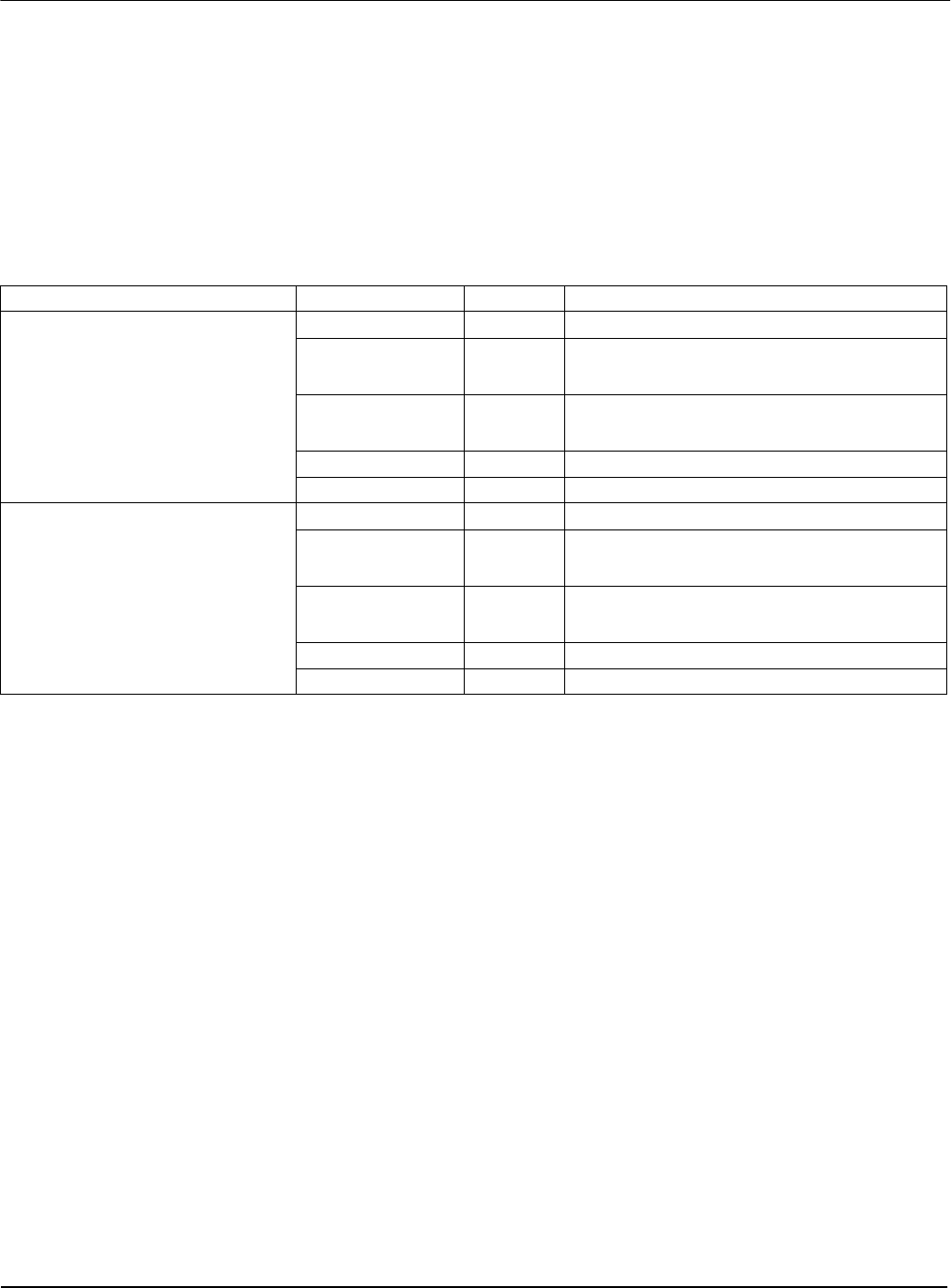

Table 4-2: TX3912 to PC Card Slots Address Remapping for Direct Connection

S1D13505 Uses PC Card Slot # Toshiba Address Size Function

1

0800 0000h 16M byte Card 1 IO or Attribute

0900 0000h 8M byte

S1D13505 registers,

aliased 4 times at 2M byte intervals

0980 0000h 8M byte

S1D13505 display buffer,

aliased 4 times at 2M byte intervals

0A00 0000h 32M byte Card 1 IO or Attribute

6400 0000h 64M byte Card 1 Memory

2

0C00 0000h 16M byte Card 2 IO or Attribute

0D00 0000h 8M byte

S1D13505 registers,

aliased 4 times at 2M byte intervals

0D80 0000h 8M byte

S1D13505 display buffer,

aliased 4 times at 2M byte intervals

0E00 0000h 32M byte Card 2 IO or Attribute

6800 0000h 64M byte Card 2 Memory