Page 108

Epson Research and Development

Vancouver Design Center

S1D13505 Programming Notes and Examples

X23A-G-003-07 Issue Date: 01/02/05

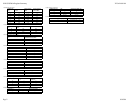

Table 12-3: Passive Dual Panel @ 640x480 with

40MHz Pixel Clock

Register

Mono 4-Bit EL

640X480@60Hz

Mono 8-Bit

640X480@60Hz

Color 8-Bit

640X480@60Hz

Color 16-Bit

640X480@60Hz

Notes

REG[02h] 1000 0010 0001 0010 0001 0110 0010 0110 set panel type

REG[03h] 0000 0000 0000 0000 0000 0000 0000 0000 set MOD rate

REG[04h] 0100 1111 0100 1111 0100 1111 0100 1111 set horizontal display width

REG[05h] 0000 0101 0000 0101 0000 0101 0000 0101 set horizontal non-display period

REG[08h] 1110 1111 1110 1111 1110 1111 1110 1111 set vertical display height bits 7-0

REG[09h] 0000 0000 0000 0000 0000 0000 0000 0000 set vertical display height bits 9-8

REG[0Ah] 0011 1110 0011 1110 0011 1110 0011 1110 set vertical non-display period

REG[0Dh] 0000 1101 0000 1101 0000 1101 0000 1101 set 8 bpp and LCD enable

REG[19h] 0000 0010 0000 0010 0000 0010 0000 0010 set MCLK and PCLK divide

REG[1Bh] 0000 0000 0000 0000 0000 0000 0000 0000 enable half frame buffer

REG[24h] 0000 0000 0000 0000 0000 0000 0000 0000 set Look-Up Table address to 0

REG[26h] load LUT load LUT load LUT load LUT load Look-Up Table

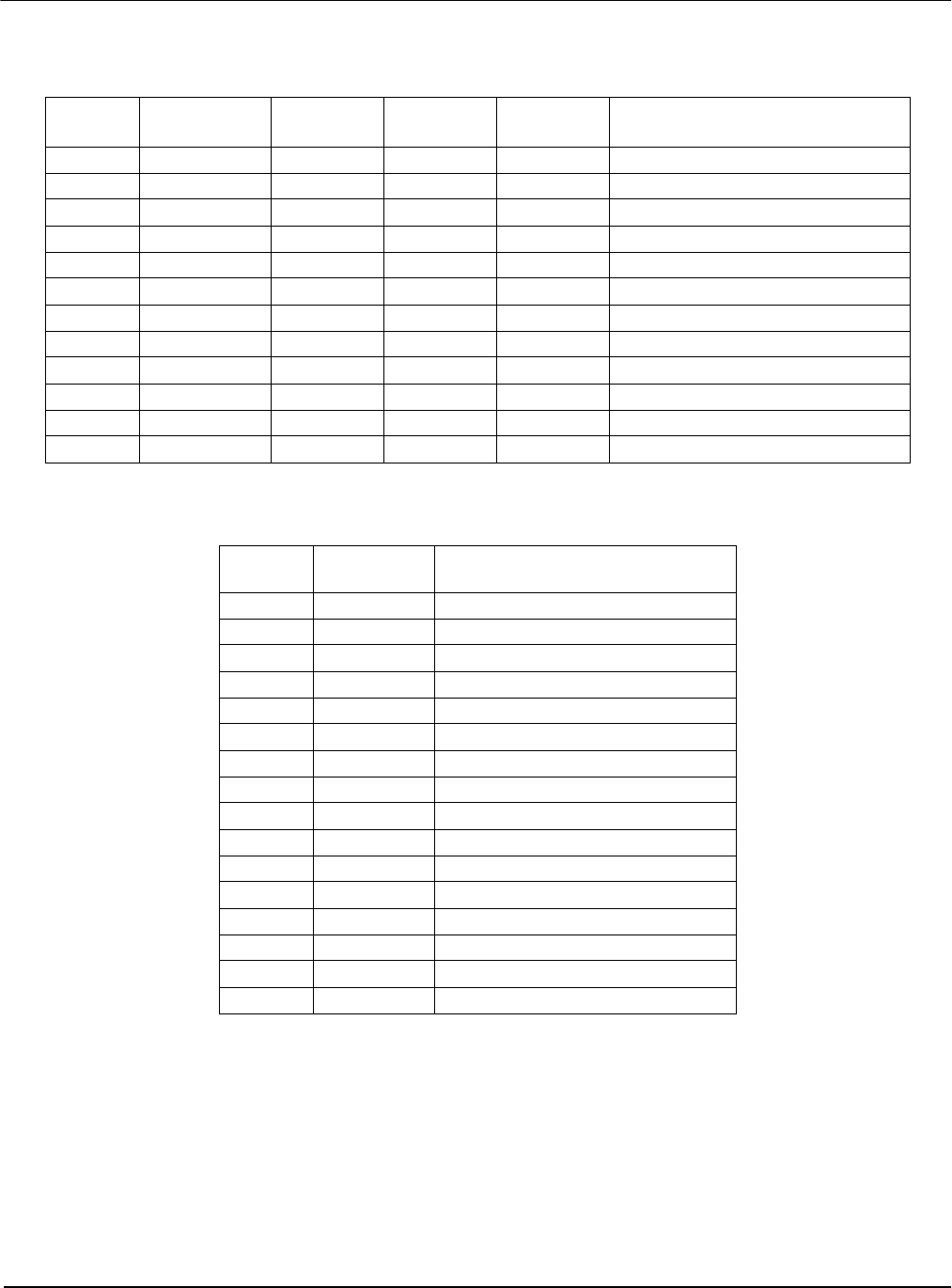

Table 12-4: TFT Single Panel @ 640x480 with

25.175 MHz Pixel Clock

Register

Color 16-Bit

640X480@60Hz

Notes

REG[02h] 0010 0101 set panel type

REG[03h] 0000 0000 set MOD rate

REG[04h] 0100 1111 set horizontal display width

REG[05h] 0001 0011 set horizontal non-display period

REG[06h] 0000 0001 set HSYNC start position

REG[07h] 0000 1011 set HSYNC polarity and pulse width

REG[08h] 1101 1111 set vertical display height bits 7-0

REG[09h] 0000 0001 set vertical display height bits 9-8

REG[0Ah] 0010 1011 set vertical non-display period

REG[0Bh] 0000 1001 set VSYNC start position

REG[0Ch] 0000 0001 set VSYNC polarity and pulse width

REG[0Dh] 0000 1101 set 8 bpp and LCD enable

REG[19h] 0000 0000 set MCLK and PCLK divide

REG[1Bh] 0000 0001 disable half frame buffer

REG[24h] 0000 0000 set Look-Up Table address to 0

REG[26h] load LUT load Look-Up Table