Epson Research and Development

Page 109

Vancouver Design Center

Hardware Functional Specification S1D13505

Issue Date: 01/02/02 X23A-A-001-14

REG[16h] bits 7-0 Memory Address Offset Bits [10:0]

REG[17h] bits 2-0 These bits form the 11-bit address offset from the starting word of line n to the starting word of line

n+1. This value is applied to both Screen 1 and Screen 2.

Note that this value is in words.

A virtual image can be formed by setting this register to a value greater than the width of the dis-

play. The displayed image is a window into the larger virtual image.

See “Section 10

Display Configuration”

for details.

This register is used to control the horizontal pixel panning of Screen 1 and Screen 2. Each screen

can be independently panned to the left by programming its respective Pixel Panning Bits to a non-

zero value. The value represents the number of pixels panned. The maximum pan value is dependent

on the display mode.

Smooth horizontal panning can be achieved by a combination of this register and the Display Start

Address registers.

See “Section 10

Display Configuration”

for details.

bits 7-4 Screen 2 Pixel Panning Bits [3:0]

Pixel panning bits for screen 2.

bits 3-0 Screen 1 Pixel Panning Bits [3:0]

Pixel panning bits for screen 1.

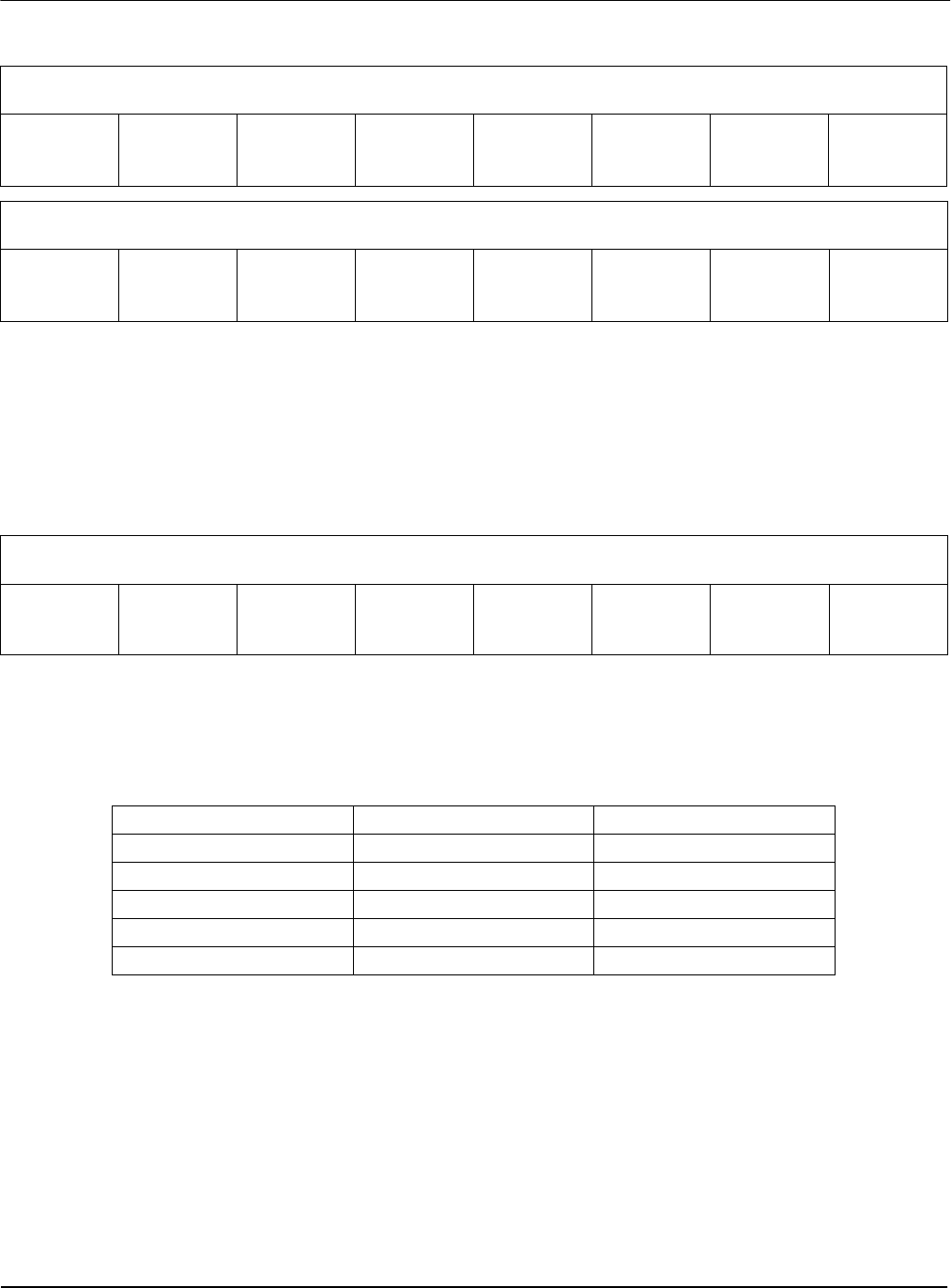

Memory Address Offset Register 0

REG[16h] RW

Memory

Address

Offset Bit 7

Memory

Address

Offset Bit 6

Memory

Address

Offset Bit 5

Memory

Address

Offset Bit 4

Memory

Address

Offset Bit 3

Memory

Address

Offset Bit 2

Memory

Address

Offset Bit 1

Memory

Address

Offset Bit 0

Memory Address Offset Register 1

REG[17h] RW

n/a n/a n/a n/a n/a

Memory

Address

Offset Bit 10

Memory

Address

Offset Bit 9

Memory

Address

Offset Bit 8

Pixel Panning Register

REG[18h] RW

Screen 2

Pixel Panning

Bit 3

Screen 2

Pixel Panning

Bit 2

Screen 2

Pixel Panning

Bit 1

Screen 2

Pixel Panning

Bit 0

Screen 1

Pixel Panning

Bit 3

Screen 1

Pixel Panning

Bit 2

Screen 1

Pixel Panning

Bit 1

Screen 1

Pixel Panning

Bit 0

Table 8-8: Pixel Panning Selection

Display Mode Maximum Pan Value Pixel Panning Bits active

1 bpp 16 Bits [3:0]

2 bpp 8 Bits [2:0]

4 bpp 4 Bits [1:0]

8 bpp 1 Bit 0

15/16 bpp 0 none