Epson Research and Development

Page 143

Vancouver Design Center

Hardware Functional Specification S1D13505

Issue Date: 01/02/02 X23A-A-001-14

4. Optimum frame rates for panels range from 60Hz to 150Hz. If the maximum refresh rate is too

high for a panel, MCLK should be reduced or PCLK should be divided down.

5. Half Frame Buffer disabled by REG[1Bh] bit 0.

6. When setting a horizontal resolution greater than 767 pixels, with a color depth of 15/16 bpp,

the Memory Offset Registers (REG[16h], REG[17h]) must be set to a virtual horizontal pixel

resolution of 1024.

14.3 Bandwidth Calculation

When calculating the average bandwidth, there are two periods that must be calculated separately.

The first period is the time when the CPU is in competition with the display refresh fetches. The CPU

can only access the memory when the display refresh releases the memory controller. The CPU

bandwidth during this period is called the “bandwidth during display period”.

The second period is the time when the CPU has full access to the memory, with no competition from

the display refresh. The CPU bandwidth during this period is called the “bandwidth during non

display period.”

To calculate the average bandwidth, calculate the percentage of time between display period and non

display period. The percentage of display period is multiplied with the bandwidth during display

period. The percentage of non display period is multiplied with the bandwidth during non display

period. The two products are summed to provide the average bandwidth.

Bandwidth during non display period

Based on simulation, it requires a minimum of 12 MCLKs to service one, two byte, CPU access to

memory. This includes all the internal handshaking and assumes that N

RC

is set to 4MCLKs and the

wait state bits are set to 10b.

Bandwidth during non display period = f(MCLK) / 6 Mb/s

Bandwidth during display period

The amount of time taken up by display refresh fetches is a function of the color depth, and the

display type. Below is a table of the number of MCLKs required for various memory fetches to

display 16 pixels. Assuming N

RC

= 4MCLKs.

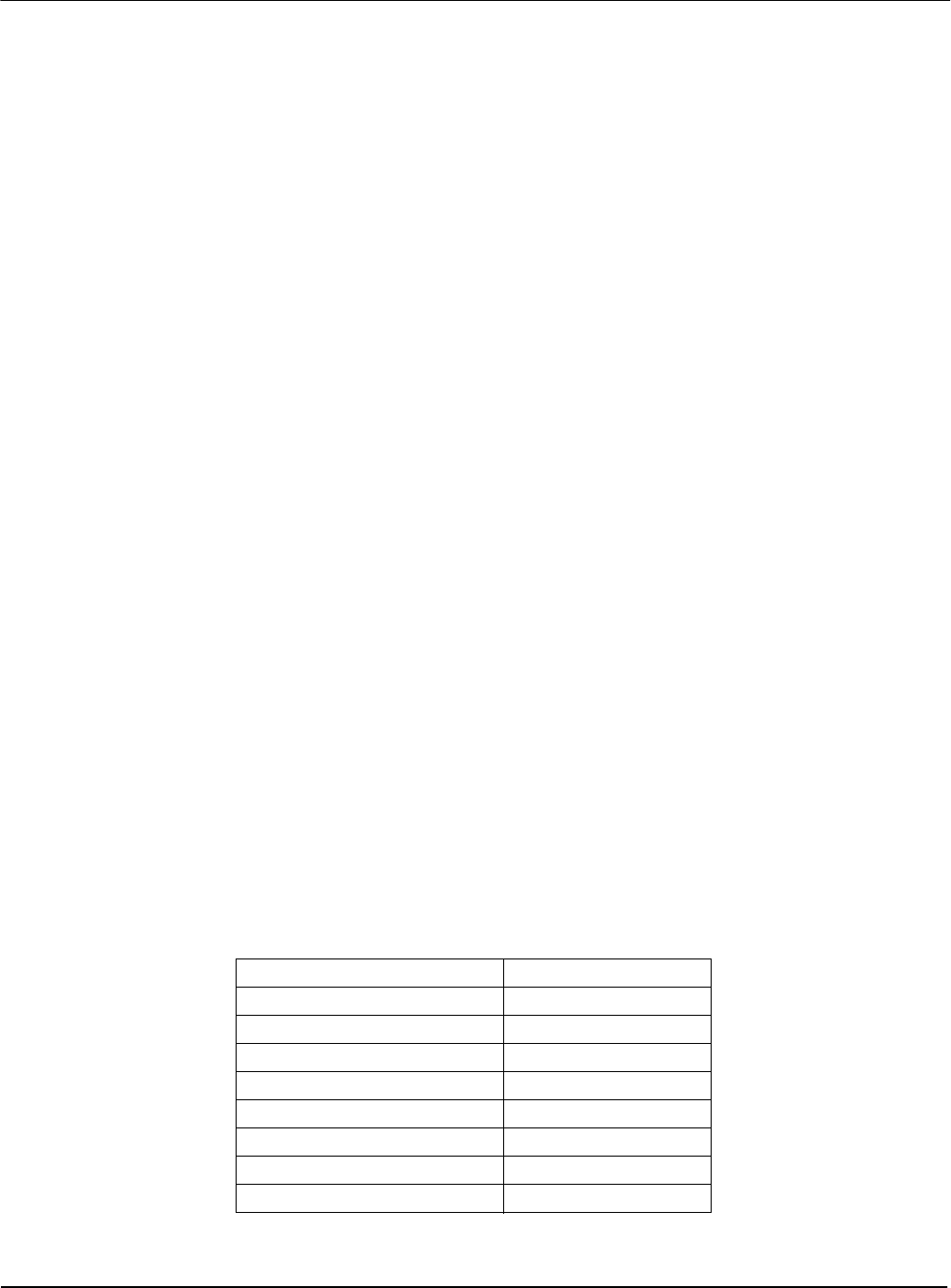

Table 14-4: Number of MCLKs required for various memory access

Memory access Number of MCLKs

Half Frame Buffer, monochrome 7

Half Frame Buffer, color 11

Display @ 1 bpp 4

Display @ 2 bpp 5

Display @ 4 bpp 7

Display @ 8 bpp 11

Display @ 16 bpp 19

CPU 4