Epson Research and Development

Page 55

Vancouver Design Center

Hardware Functional Specification S1D13505

Issue Date: 01/02/02 X23A-A-001-14

1. If the S1D13505 host interface is disabled, the timing for IOCHRDY driven low is relative to

the falling edge of MEMR#, MEMW# or

the first positive edge of BUSCLK after LatchA20,

SA[19:0], M/R# becomes valid, whichever one is later.

2. If the S1D13505 host interface is disabled, the timing for SD[15:0] driven is relative to the

falling edge of MEMR# or

the first positive edge of BUSCLK after LatchA20, SA[19:0],

M/R# becomes valid, whichever one is later.

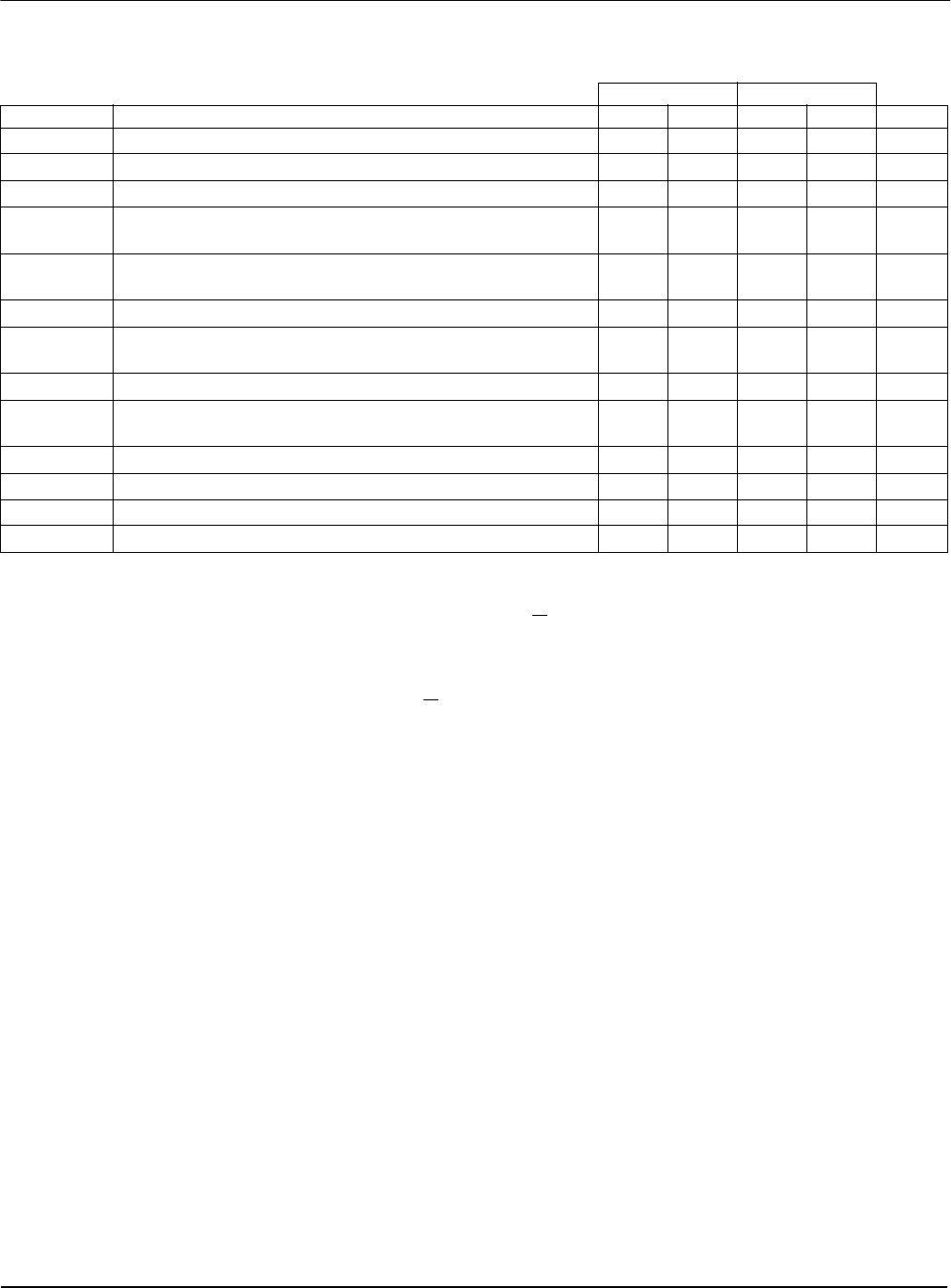

Table 7-7: MIPS/ISA Timing

3.0V 5.0V

Symbol Parameter Min Max Min Max Units

t1

Clock period

20 20 ns

t2

Clock pulse width high

66ns

t3

Clock pulse width low

66ns

t4

LatchA20, SA[19:0], M/R#, SBHE# setup to first BUSCLK where

CS# = 0 and either MEMR# = 0 or MEMW# = 0

10 10 ns

t5

LatchA20, SA[19:0], M/R#, SBHE# hold from rising edge of

either MEMR# or MEMW#

00ns

t6

CS# hold from rising edge of either MEMR# or MEMW#

00ns

t7

1

Falling edge of either MEMR# or MEMW# to IOCHRDY# driven

low

00ns

t8

Rising edge of either MEMR# or MEMW# to IOCHRDY# tri-state

5252.510ns

t9

SD[15:0] setup to third BUSCLK where CS# = 0 MEMW# = 0

(write cycle)

10 10 ns

t10

SD[15:0] hold (write cycle)

00ns

t11

2

Falling edge MEMR# to SD[15:0] driven (read cycle)

00ns

t12

SD[15:0] setup to rising edge IOCHRDY# (read cycle)

00ns

t13

Rising edge of MEMR# toSD[15:0] tri-state (read cycle)

525510ns