Epson Research and Development

Page 91

Vancouver Design Center

Hardware Functional Specification S1D13505

Issue Date: 01/02/02 X23A-A-001-14

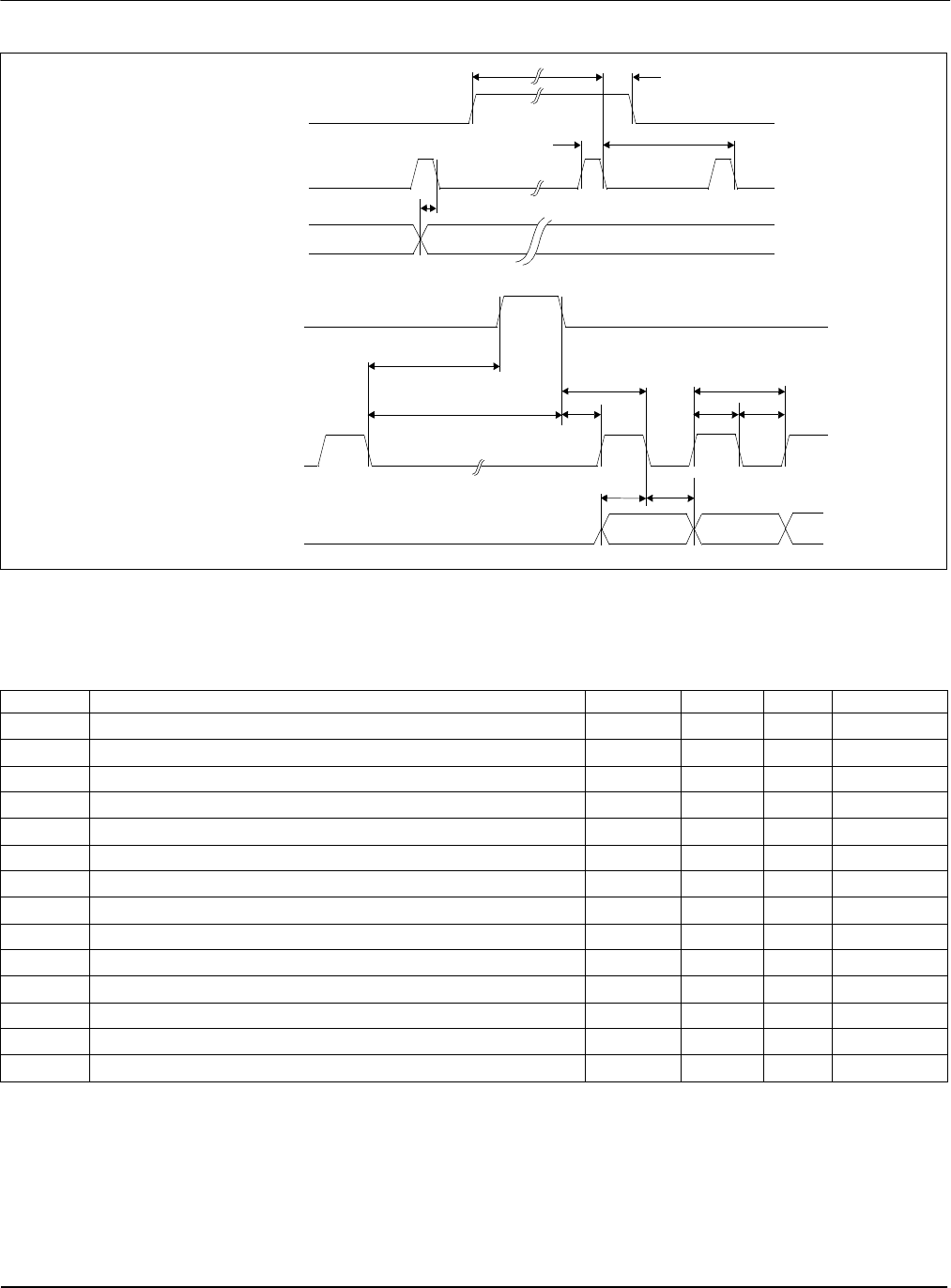

Figure 7-39: 8-Bit Dual Color Passive LCD Panel A.C. Timing

1. Ts = pixel clock period = memory clock, [memory clock]/2, [memory clock]/3, [memory clock]/4 (see REG[19h] bits [1:0])

2. t1

min

= t3

min

- 14Ts

3. t3

min

= [((REG[04h] bits [6:0])+1)*8 + ((REG[05h] bits [4:0]) + 1)*8] + 33 Ts

4. t5

min

= [(((REG[04h] bits [6:0])+1)*8 + ((REG[05h] bits [4:0]) + 1)*8)-1] Ts

5. t6

min

= [((REG[05h] bits [4:0]) + 1)*8 - 20] Ts

6. t7

min

= [((REG[05h] bits [4:0]) + 1)*8 - 11] Ts

Table 7-30: 8-Bit Dual Color Passive LCD Panel A.C. Timing

Symbol Parameter Min Typ Max Units

t1

FPFRAME setup to FPLINE pulse trailing edge

note 2

t2

FPFRAME hold from FPLINE pulse trailing edge

14 Ts (note 1)

t3

FPLINE period

note 3

t4

FPLINE pulse width

9Ts

t5

MOD transition to FPLINE pulse trailing edge

1note 4Ts

t6

FPSHIFT falling edge to FPLINE pulse leading edge

note 5

t7

FPSHIFT falling edge to FPLINE pulse trailing edge

note 6

t8

FPLINE pulse trailing edge to FPSHIFT falling edge

t14 + t11 Ts

t9

FPSHIFT period

1Ts

t10

FPSHIFT pulse width low

0.45 Ts

t11

FPSHIFT pulse width high

0.45 Ts

t12

UD[3:0], LD[3:0] setup to FPSHIFT falling edge

0.45 Ts

t13

UD[3:0], LD[3:0] hold to FPSHIFT falling edge

0.45 Ts

t14

FPLINE pulse trailing edge to FPSHIFT rising edge

13 Ts

t12 t13

t14

t8 t9

t10t11

12

Data Timing

FPFRAME

t1 t2

t3

t5

t4

FPLINE

MOD

Sync Timing

FPLINE

FPSHIFT

t7

t6

UD[3:0]

LD[3:0]