Page 72

Epson Research and Development

Vancouver Design Center

S1D13505 Hardware Functional Specification

X23A-A-001-14 Issue Date: 01/02/02

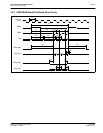

7.3.5 FPM-DRAM CAS Before RAS Refresh Timing

Figure 7-20: FPM-DRAM CAS Before RAS Refresh Timing

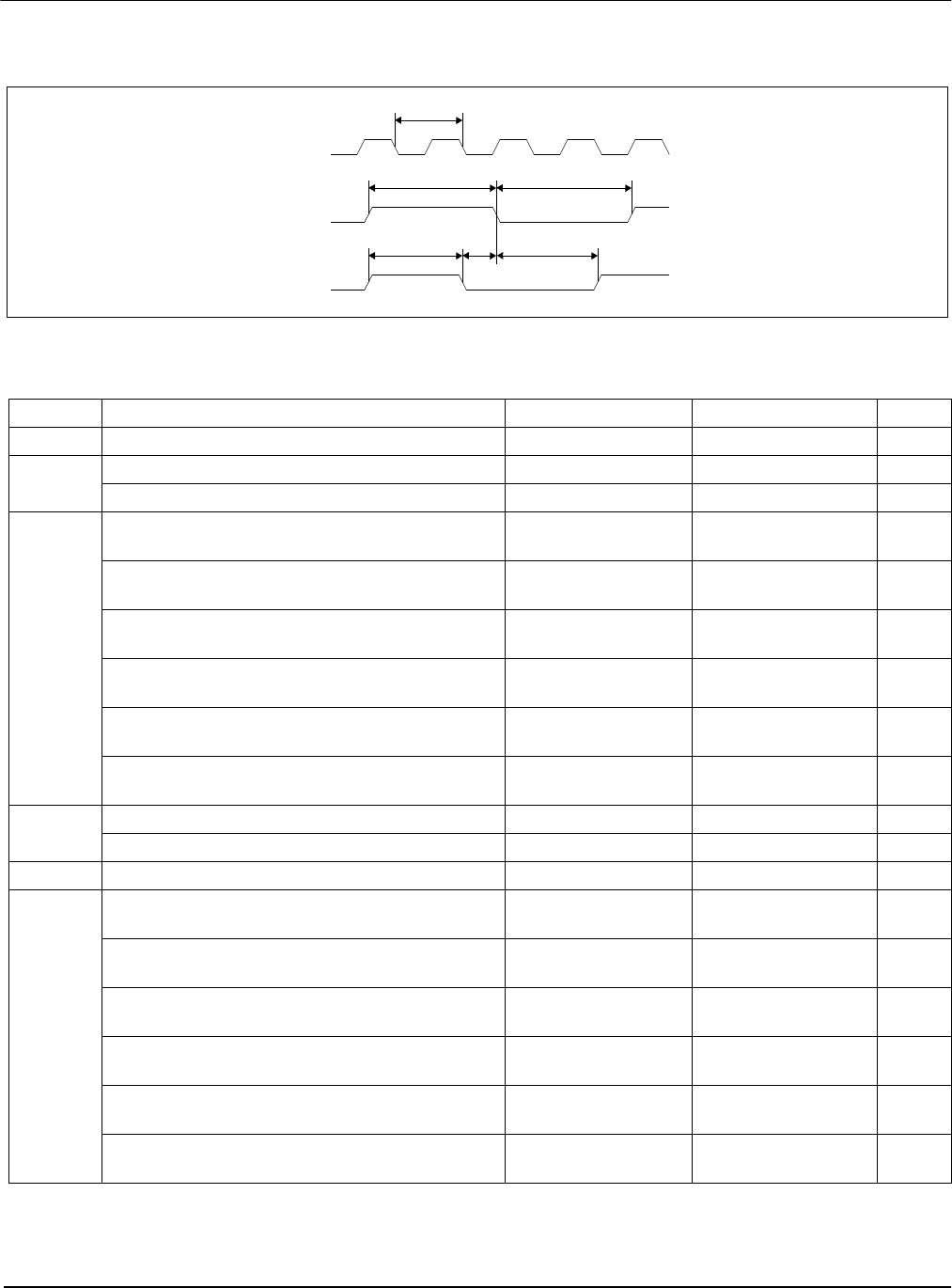

Table 7-19: FPM-DRAM CAS Before RAS Refresh Timing

Symbol Parameter Min Max Units

t1 Internal memory clock period 40 ns

t2

RAS# precharge time (REG[22h] bits 3-2 = 00) 2.45 t1 - 3 ns

RAS# precharge time (REG[22h] bits 3-2 = 01 or 10) 1.45 t1 - 3 ns

t3

RAS# pulse width (REG[22h] bits 6-5 = 00 and bits 3-

2 = 00)

2.45 t1 - 3 ns

RAS# pulse width (REG[22h] bits 6-5 = 00 and bits 3-

2 = 01 or 10)

3.45 t1 - 3 ns

RAS# pulse width (REG[22h] bits 6-5 = 01 and bits 3-

2 = 00)

1.45 t1 - 3 ns

RAS# pulse width (REG[22h] bits 6-5 = 01 and bits 3-

2 = 01 or 10)

2.45 t1 - 3 ns

RAS# pulse width (REG[22h] bits 6-5 = 10 and bits 3-

2 = 00)

0.45 t1 - 3 ns

RAS# pulse width (REG[22h] bits 6-5 = 10 and bits 3-

2 = 01 or 10)

1.45 t1 - 3 ns

t4

CAS# pulse width (REG[22h] bits 3-2 = 00) 2 t1 - 3 ns

CAS# pulse width (REG[22h] bits 3-2 = 01 or 10) 1 t1 - 3

t5 CAS# Setup to RAS# 0.45 t1 - 3 ns

t6

CAS# Hold to RAS# (REG[22h] bits 6-5 = 00 and bits

3-2 = 00)

2.45 t1 - 3 ns

CAS# Hold to RAS# (REG[22h] bits 6-5 = 00 and bits

3-2 = 01 or 10)

3.45 t1 - 3 ns

CAS# Hold to RAS# (REG[22h] bits 6-5 = 01 and bits

3-2 = 00)

1.45 t1 - 3 ns

CAS# Hold to RAS# (REG[22h] bits 6-5 = 01 and bits

3-2 = 01 or 10)

2.45 t1 - 3 ns

CAS# Hold to RAS# (REG[22h] bits 6-5 = 10 and bits

3-2 = 00)

0.45 t1 - 3 ns

CAS# Hold to RAS# (REG[22h] bits 6-5 = 10 and bits

3-2 = 01 or 10)

1.45 t1 - 3 ns

RAS#

CAS#

t2 t3

t1

Memory

Clock

t4 t5

t6