Epson Research and Development

Page 17

Vancouver Design Center

Evaluation Board User Manual S5U13505-D9000

Issue Date: 01/02/05 X23A-G-002-04

3.1.2 Memory Address (CS#, M/R#) Decoding

The S1D13505 is a memory-mapped device for both the registers and the display buffer access. The

specific memory address is solely controlled by the CS# and M/R# decode logic. The memory space

requirements are:

• A 2M byte linear address range for the display buffer.

• 47 bytes for the registers.

With the FPGA code that comes with this board, the registers are located at 0x12000000 and the

display buffer is located at 0x12200000.

3.2 FPGA Code Functionality

The D9000/ODO is a flexible hardware/software development system designed for use with the

Microsoft Windows CE operating system. It is designed so that an arbitrary set of peripherals may

be quickly compiled in a way that is identical to the final product. A 100K FPGA is at the center of

the system and sits between the CPU and all other peripherals. Most peripherals, except analog

components, are implemented within the FPGA.

In order to support several different CPUs, any peripherals that connect to the system have to use a

common Register Interface. This interface is similar to a standard bus, in that it allows the CPU to

read and write registers associated with the peripheral. For each peripheral, whether implemented

internal or external to the FPGA, a VHDL module has to be written to implement the register

interface and to assign the necessary signals to the slot where the peripheral is going to be located.

The D9000/ODO platform supports 32-bit accesses to peripherals. The S1D13505 provides a 16-bt

CPU interface, and therefore, the FPGA files provided with the S5U13505-D9000 convert any 32-

bit accesses to back-to-back 16-bit cycles.

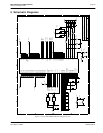

3.3 Board Dimensions

To obtain the required number of interface signals, the S5U13505-D9000 utilizes two SmallTypeZ

slots (6 and 7). Board dimensions are 2.65 x 3.20cm with both the CRT and LCD connectors acces-

sible on the outside edge.