Epson Research and Development

Page 61

Vancouver Design Center

Hardware Functional Specification S1D13505

Issue Date: 01/02/02 X23A-A-001-14

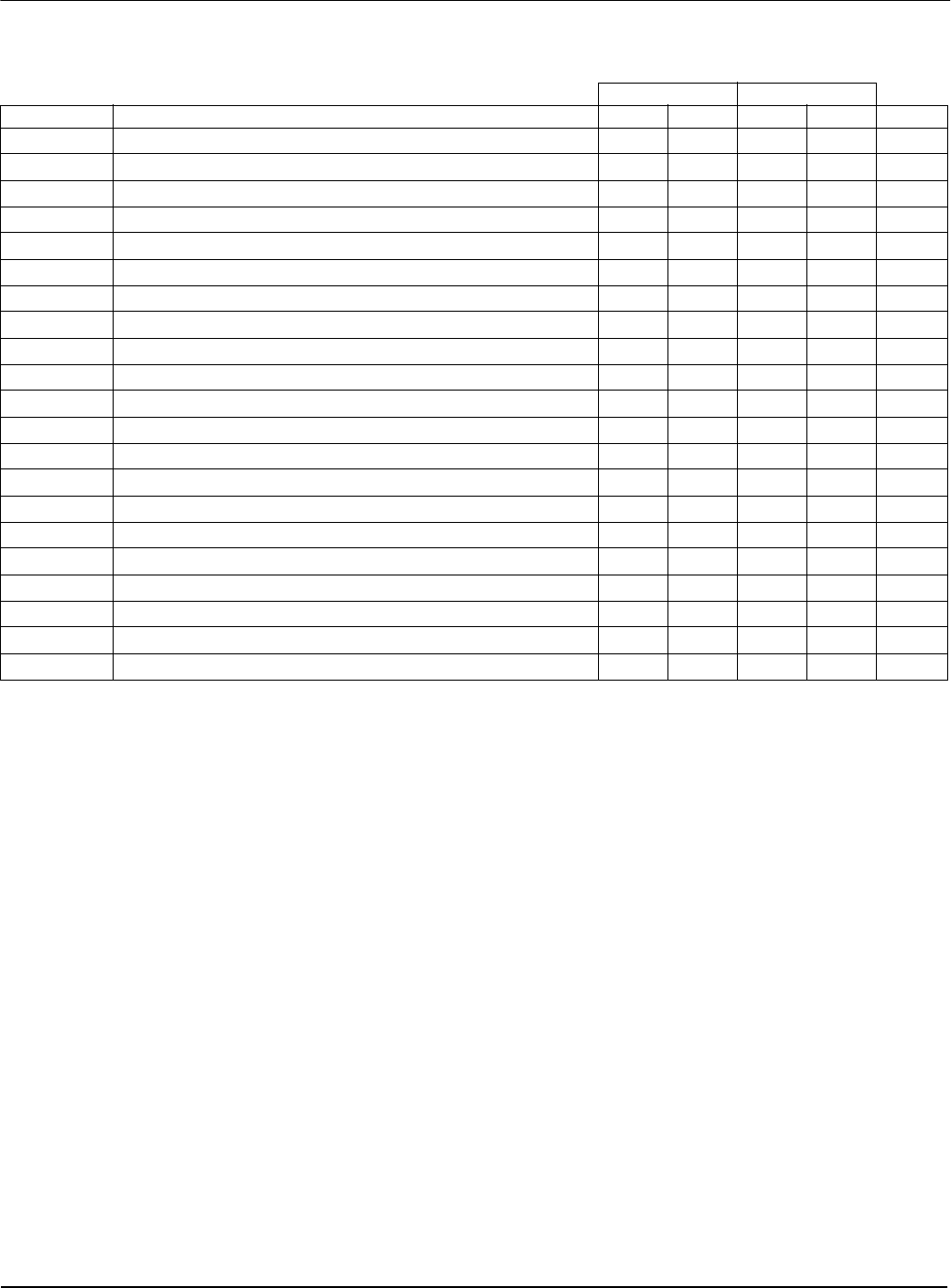

Table 7-12: Power PC Timing

3.0V 5.0V

Symbol Parameter Min Max Min Max Units

t1

Clock period

25 20 ns

t2

Clock pulse width low

66ns

t3

Clock pulse width high

66ns

t4

AB[11:31], RD/WR#, TSIZ[0:1], M/R# setup

10 10 ns

t5

AB[11:31], RD/WR#, TSIZ[0:1], M/R# hold

00ns

t6

CS# setup

10 10 ns

t7

CS# hold

00ns

t8

TS# setup

710ns

t9

TS# hold

50ns

t10

CLKOUT to TA# driven

00ns

t11

CLKOUT to TA# low

319312ns

t12

CLKOUT to TA# high

319.73 13 ns

t13

negative edge CLKOUT to TA# tri-state

5252.510ns

t14

CLKOUT to BI# driven

018011ns

t15

CLKOUT to BI# high

316310ns

t16

negative edge CLKOUT to BI# tri-state

5252.510ns

t17

D[0:15] setup to 2nd CLKOUT after TS# = 0 (write cycle)

10 10 ns

t18

D[0:15] hold (write cycle)

00ns

t19

CLKOUT to D[0:15] driven (read cycle)

00ns

t20

D[0:15] valid to TA# falling edge (read cycle)

00ns

t21

CLKOUT to D[0:15] tri-state (read cycle)

5252.510ns