Page 20

Epson Research and Development

Vancouver Design Center

S5U13505-D9000 Evaluation Board User Manual

X23A-G-002-04 Issue Date: 01/02/05

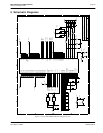

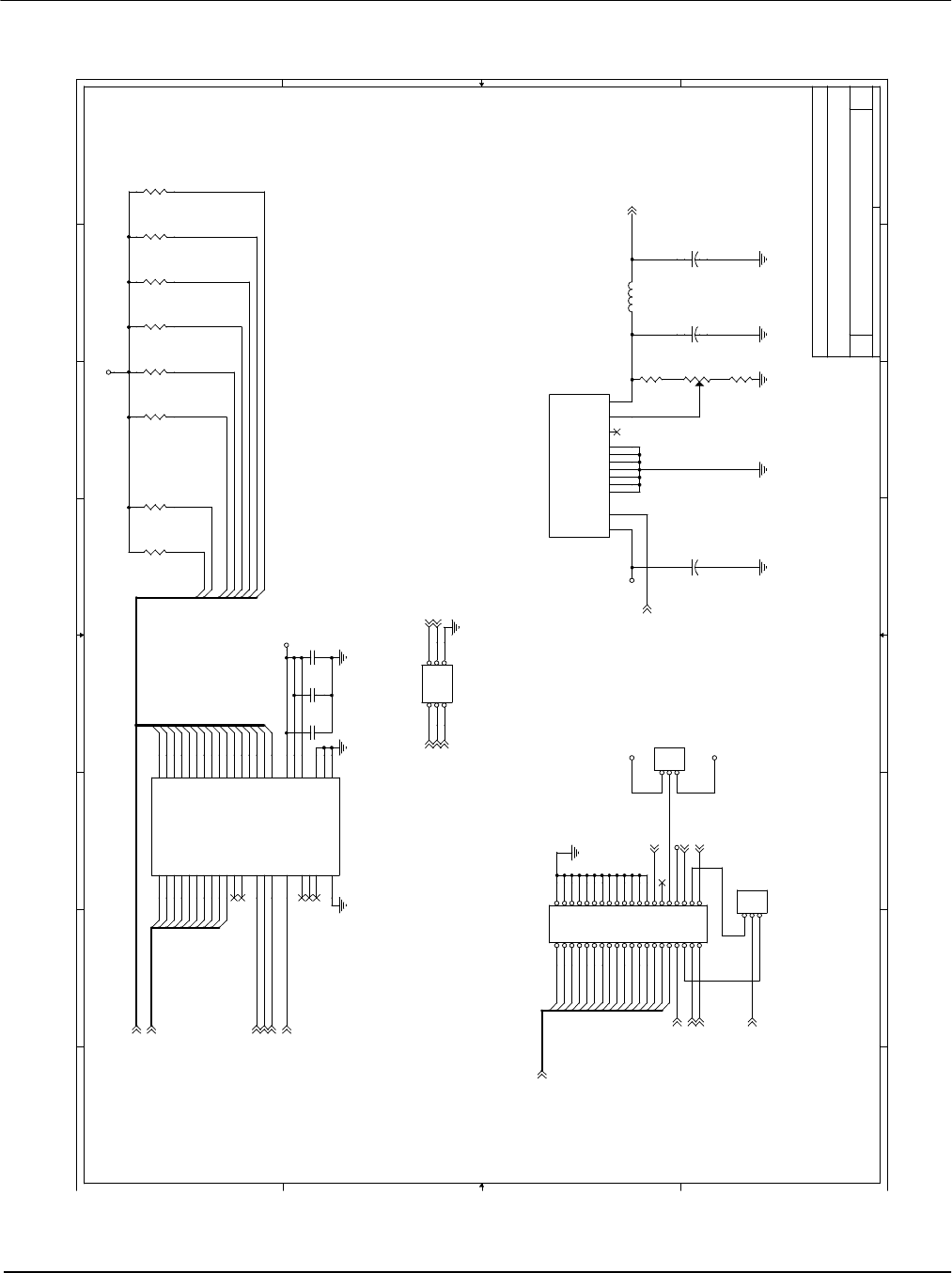

Figure 5-2: S5U13505-D9000 Schematic Diagram (2 of 3)

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

D D

C

C

B

B

A

A

LCD bias generator

Touchs creen connector

LCD conne ctor

MD[12:0] = 0, 0, 1, 1, X, 01, 0, 1, 011, 0, meaning:

busclk/1, primary host bus, lcdpwr#,

pin 71 = gpo#, symmetrical 1M x 16 DRAM,

wait#, Little Endian, generic 16-bit bus.

6.0

S5U13505-D9000

B

23Monday, February 23, 1998

EPSON RESEARCH AND DEVE LOPMENT INC.

Title

Size Document Number Rev

Date: Sheet

of

MA[0..9]

MD[0..15]

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

MD1

MD2

MD4

MD6

MD9

MD10

FPDAT[0..15]

FPDAT0

FPDAT1

FPDAT2

FPDAT3

FPDAT4

FPDAT5

FPDAT6

FPDAT7

FPDAT8

FPDAT9

FPDAT10

FPDAT11

FPDAT12

FPDAT13

FPDAT14

FPDAT15

CK2

MD5

MD3

RAS#

MA[0..9]

WE#

UCAS#

MD[0..15]

LCAS#

VDDH

FPDAT[0..15]

FPSHIFT

FPSHIFT2

FPLINE

FPFRAME

LCDBACK#

XL

YU

LCDPWR#

XY

XR

YL

VDDH

LCDPWR#

DC3V

DC3V

DC5V

DC12V

DC5V

DC3V

U2

DRAM1MX16-SOJ-3.3V

A0

17

A1

18

A2

19

A3

20

A4

23

A5

24

A6

25

A7

26

A8R/A8

27

A9R/A9

28

A10/NC

16

A11/NC

15

/RAS

14

/UCAS

30

/LCAS

31

/W

13

NC

11

NC

12

NC

32

/OE

29

DQ0

2

DQ1

3

DQ2

4

DQ3

5

DQ4

7

DQ5

8

DQ6

9

DQ7

10

DQ8

33

DQ9

34

DQ10

35

DQ11

36

DQ12

38

DQ13

39

DQ14

40

DQ15

41

VCC

1

VCC

6

VCC

21

VSS

22

VSS

37

VSS

42

R1

15K

R2

15K

R5

15K

R6

15K

R7

15K

R8

15K

C7

0.1uF

C8

0.1uF

C9

0.1uF

L6

1uH

R17

15K

+

C18

22uF/63V

+

C20

10uF/63V

+

C17

47uF/10V

U4

RD-0412

VOUT_ADJ

1

DC_IN

2

REMOTE

3

GND

4

GND

5

GND

6

GND

7

GND

8

NC

9

GND

10

GND

11

DC_OUT

12

LCD1

HEADER 20X2

1 2

3 4

5 6

7 8

9 10

11 12

13 14

15 16

17 18

19 20

21 22

23 24

25 26

27 28

29 30

31 32

33 34

35 36

37 38

39 40

FPS2

HEADER 3

1

2

3

LCDVCC1

HEADER 3

1

2

3

TS1

HEADER 3X2

1 2

3 4

5 6

R16

200K

R15

470K

R26

n/p

R25

n/p

POT