Epson Research and Development

Page 13

Vancouver Design Center

Interfacing to the NEC V832™ Microprocessor S1D13505

Issue Date: 01/02/05 X23A-G-012-02

4.2 S1D13505 Hardware Configuration

The S1D13505 latches MD15 through MD0 to allow selection of the bus mode and other

configuration data on the rising edge of RESET#. For details on configuration, refer to the

S1D13505 Hardware Functional Specification, document number X23A-A-001-xx.

The table below shows those configuration settings relevant to the PC Card host bus

interface used by the NEC V832 microprocessor.

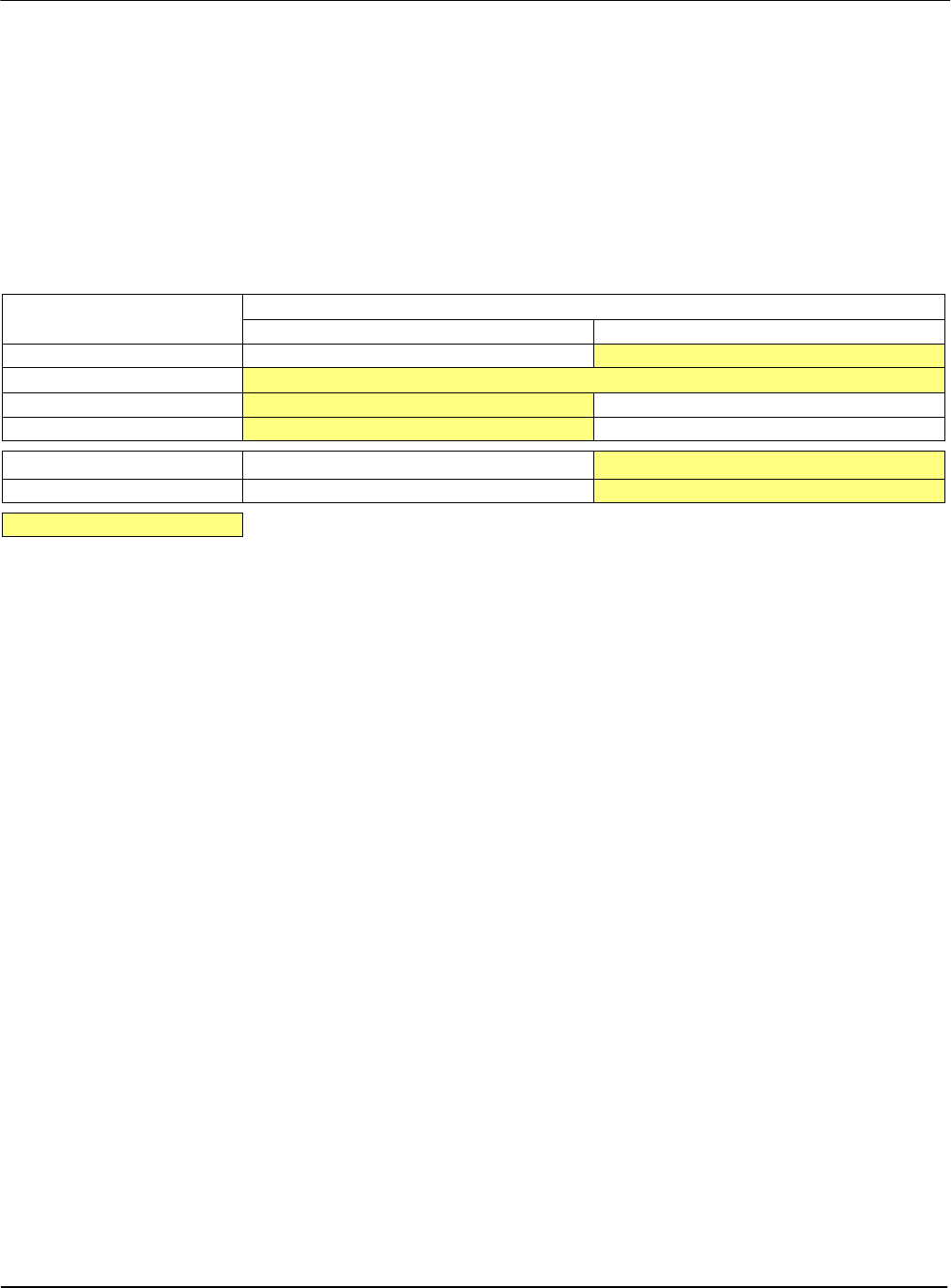

Table 4-1: Summary of Power-On/Reset Options

S1D13505

Pin Name

Value on this pin at rising edge of RESET# is used to configure: (1/0)

10

MD0 8-bit host bus interface

16-bit host bus interface

MD[3:1] 111 = PC Card host bus interface

MD4 Little Endian Big Endian

MD5

WAIT# is active high (1 = insert wait state) WAIT# is active low (0 = insert wait state)

MD11

Alternate Host Bus Interface Selected

Primary Host Bus Interface Selected

MD12 BUSCLK input divided by two

BUSCLK input not divided by two

= configuration for NEC V832 microprocessor