Epson Research and Development

Page 139

Vancouver Design Center

Hardware Functional Specification S1D13505

Issue Date: 01/02/02 X23A-A-001-14

14 Clocking

14.1 Maximum MCLK: PCLK Ratios

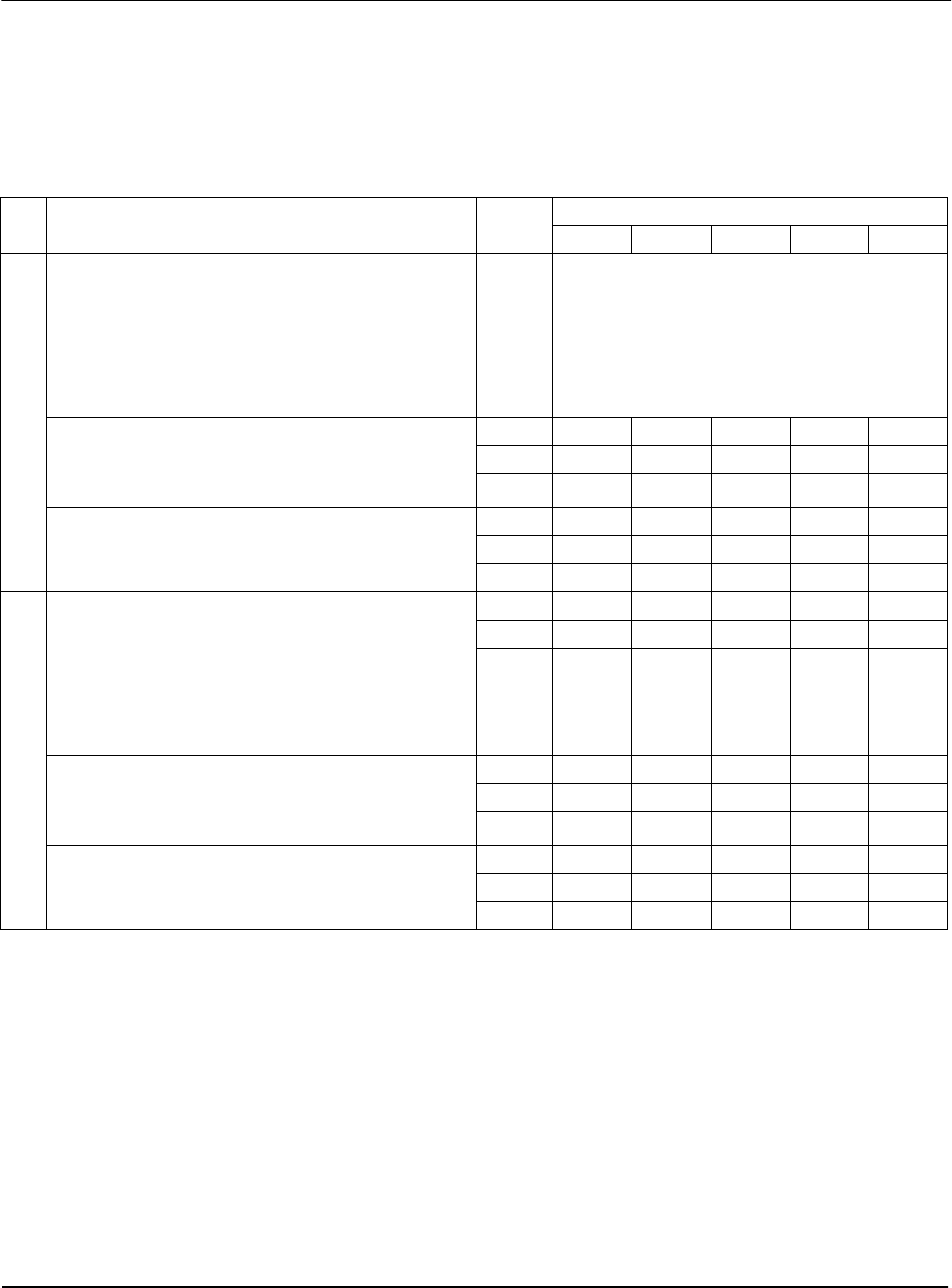

Table 14-1: Maximum PCLK Frequency with EDO-DRAM

Ink Display type

N

RC

Maximum PCLK Allowed

1 bpp 2 bpp 4 bpp 8 bpp 16 bpp

off

• Single Panel.

•CRT.

• Dual Monochrome/Color Panel with Half Frame Buffer

Disabled.

• Simultaneous CRT + Single Panel.

• Simultaneous CRT + Dual Monochrome/Color Panel

with Half Frame Buffer Disabled.

5, 4, 3 MCLK

• Dual Monochrome Panel with Half Frame Buffer

Enabled.

• Simultaneous CRT + Dual Monochrome Panel with

Half Frame Buffer Enable.

5 MCLK/2 MCLK/2 MCLK/2 MCLK/2 MCLK/3

4 MCLK/2 MCLK/2 MCLK/2 MCLK/2 MCLK/3

3 MCLK MCLK MCLK/2 MCLK/2 MCLK/2

• Dual Color Panel with Half Frame Buffer Enabled.

• Simultaneous CRT + Dual Color Panel with Half

Frame Buffer Enable.

5 MCLK/2 MCLK/2 MCLK/2 MCLK/3 MCLK/3

4 MCLK/2 MCLK/2 MCLK/2 MCLK/2 MCLK/3

3 MCLK/2 MCLK/2 MCLK/2 MCLK/2 MCLK/3

on

• Single Panel.

•CRT.

• Dual Monochrome/Color Panel with Half Frame Buffer

Disabled.

• Simultaneous CRT + Single Panel.

• Simultaneous CRT + Dual Monochrome/Color Panel

with Half Frame Buffer Disabled.

5 MCLK/2 MCLK/2 MCLK/2 MCLK/2 MCLK/3

4 MCLK MCLK MCLK/2 MCLK/2 MCLK/2

3 MCLK MCLK MCLK MCLK/2 MCLK/2

• Dual Monochrome Panel with Half Frame Buffer

Enabled.

• Simultaneous CRT + Dual Monochrome Panel with

Half Frame Buffer Enable.

5 MCLK/2 MCLK/3 MCLK/3 MCLK/3 MCLK/3

4 MCLK/2 MCLK/2 MCLK/2 MCLK/3 MCLK/3

3 MCLK/2 MCLK/2 MCLK/2 MCLK/2 MCLK/3

• Dual Color Panel with Half Frame Buffer Enabled.

• Simultaneous CRT + Dual Color Panel with Half

Frame Buffer Enable.

5 MCLK/3 MCLK/3 MCLK/3 MCLK/3 MCLK/4

4 MCLK/2 MCLK/2 MCLK/3 MCLK/3 MCLK/3

3 MCLK/2 MCLK/2 MCLK/2 MCLK/2 MCLK/3