Epson Research and Development

Page 111

Vancouver Design Center

Hardware Functional Specification S1D13505

Issue Date: 01/02/02 X23A-A-001-14

bit 3 LCD Power Disable

This bit is used to override the panel on/off sequencing logic.

When this bit = 0 the LCDPWR output is controlled by the panel on/off sequencing logic.

When this bit = 1 the LCDPWR output is directly forced to the off state.

The LCDPWR “On/Off” polarity is configured by MD10 at the rising edge of RESET# (MD10 = 0

configures LCDPWR = 0 as the Off state; MD10 = 1 configures LCDPWR = 1 as the Off state).

bits 2-1 Suspend Refresh Select Bits [1:0]

These bits specify the type of DRAM refresh to use in Suspend mode.

Note

These bits should not be changed while suspend mode is active.

bit 0 Software Suspend Mode Enable

When this bit = 1 software Suspend mode is enabled.

When this bit = 0 software Suspend mode is disabled.

See

Section 15 Power Save Modes

for details.

8.2.7 Miscellaneous Registers

bit 7 Host Interface Disable

This bit is set to 1 during power-on/reset.

This bit must be programmed to 0 to enable the Host Interface. When this bit is high, all memory

and all registers except REG[1Ah] (read-only) and REG[1Bh] are inaccessible.

bit 0 Half Frame Buffer Disable

This bit is used to disable the Half Frame Buffer.

When this bit = 1, the Half Frame Buffer is disabled.

When this bit = 0, the Half Frame Buffer is enabled.

When a single panel is selected, the Half Frame Buffer is automatically disabled and this bit has no

effect.

The half frame buffer is needed to fully support dual panels. Disabling the Half Frame Buffer

reduces memory bandwidth requirements and increases the supportable pixel clock frequency, but

results in reduced contrast on the LCD panel (the duty cycle of the LCD is halved). This mode is

not normally used except under special circumstances such as simultaneous display on a CRT and

dual panel LCD. When this mode is used the Alternate Frame Rate Modulation scheme should be

used (see REG[31h]). For details on Frame Rate calculation see Section 14.2, “Frame Rate Calcu-

lation” on page 141.

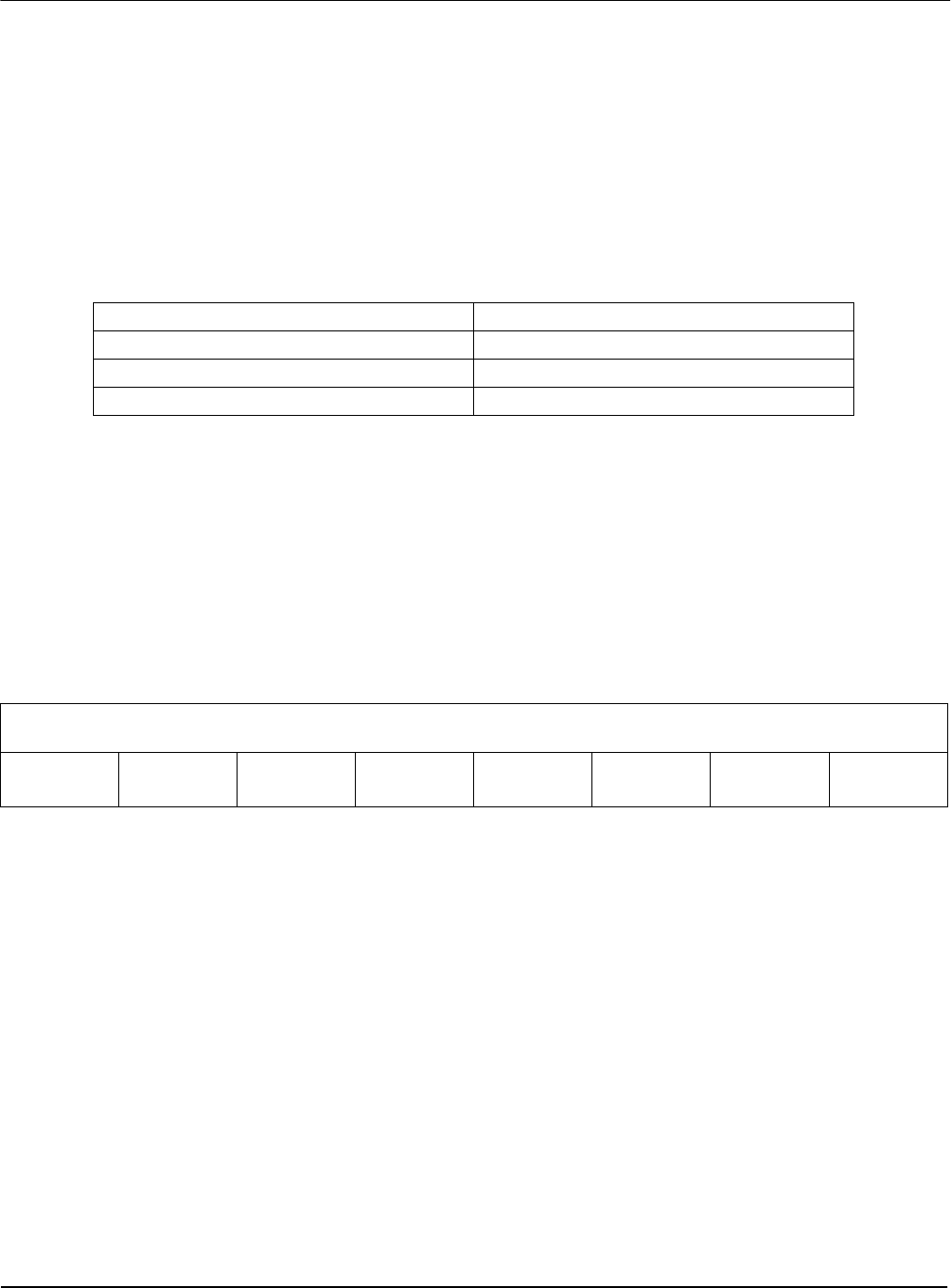

Table 8-10: Suspend Refresh Selection

Suspend Refresh Select Bits [1:0] DRAM Refresh Type

00 CAS-before-RAS (CBR) refresh

01 Self-Refresh

1X No Refresh

Miscellaneous Register

REG[1Bh] RW

Host Interface

Disable

n/an/an/an/an/an/a

Half Frame

Buffer Disable