Page 12

Epson Research and Development

Vancouver Design Center

S1D13505 Interfacing to the NEC VR4121™ Microprocessor

X23A-G-011-04 Issue Date: 01/02/05

4 V

R

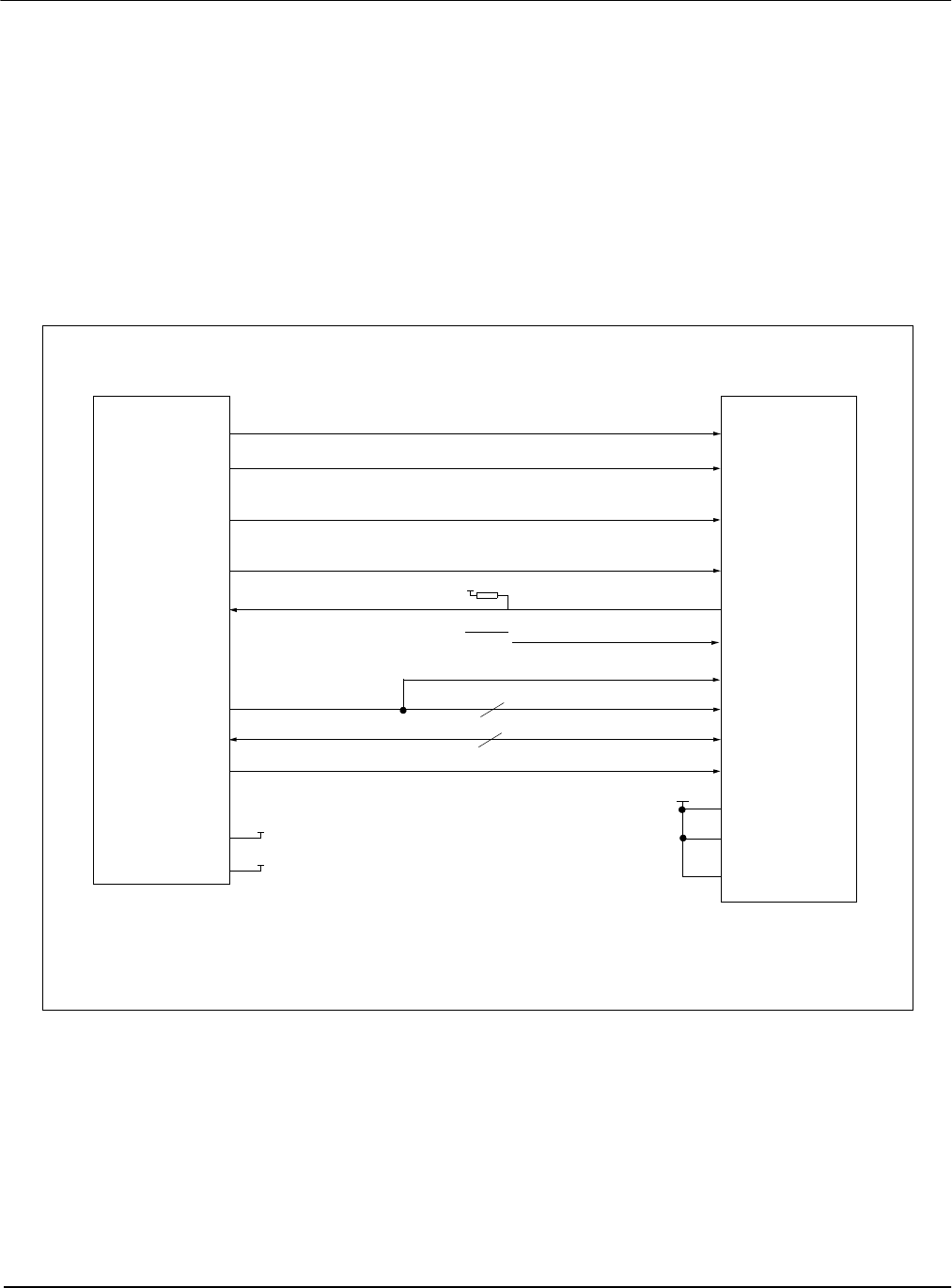

4121 to S1D13505 Interface

4.1 Hardware Description

The NEC V

R

4121 microprocessor is specifically designed to support an external LCD

controller. It provides all the necessary internal address decoding and control signals

required by the S1D13505.

The diagram below shows a typical implementation utilizing the S1D13505.

Figure 4-1: NEC V

R

4121 to S1D13505 Configuration Schematic

Note

For pin mapping see Table 3-1:, “Host Bus Interface Pin Mapping,” on page 10.

WE1#

WE0#

DB[15:0]

WAIT#

RD#

BUSCLK

S1D13505

CS#

M/R#

RESET#

AB[20:0]

ADD21

SHB#

WR#

DAT[15:0]

LCDCS#

RD#

BUSCLK

LCDRDY

ADD[25:0]

NEC V

R

4121

Pull-up

BS#

RD/WR#

V

DD

(+3.3V)

System RESET

V

DD

V

DD

3

+3.3V

+2.5V

V

DD

2

Note:

When connecting the S1D13505 RESET# pin, the system designer should be aware of all

conditions that may reset the S1D13505 (e.g. CPU reset can be asserted during wake-up

from power-down modes, or during debug states).