3-38 Intel® PXA255 Processor Developer’s Manual

Clocks and Power Manager

3.6.3 Oscillator Configuration Register (OSCC)

The OSCC, shown in Table 3-22, controls the 32.768 kHz oscillator configuration. It contains two

bits, the set-only 32.768 KHz OSCC[OON] and the read-only 32.768 kHz OSCC[OOK].

OSCC[OON] enables the external 32.768 kHz oscillator and can only be set by software. When the

oscillator is enabled, it takes up to 10 seconds for to stabilize. When the oscillator is stabilized, the

processor sets OSCC[OOK].

When OSCC[OOK] is set, the RTC and PM are clocked from the 32.768 KHz oscillator.

Otherwise, the 3.6864 MHz oscillator is used. The OPDE bit, which allows the 3.6864 MHz

oscillator to be disabled in sleep mode, is ignored (treated as if it were clear) if OSCC[OOK] is

clear. OSCC[OOK] can only be reset by a hardware reset.

This is a read/write register. Ignore reads from reserved bits. Write zeros to reserved bits.

3.7 Coprocessor 14: Clock and Power Management

Coprocessor 14 contains two registers that control the power modes and sequences:

• CP14 register 6 – CCLKCFG register

• CP14 register 7 – PWRMODE register

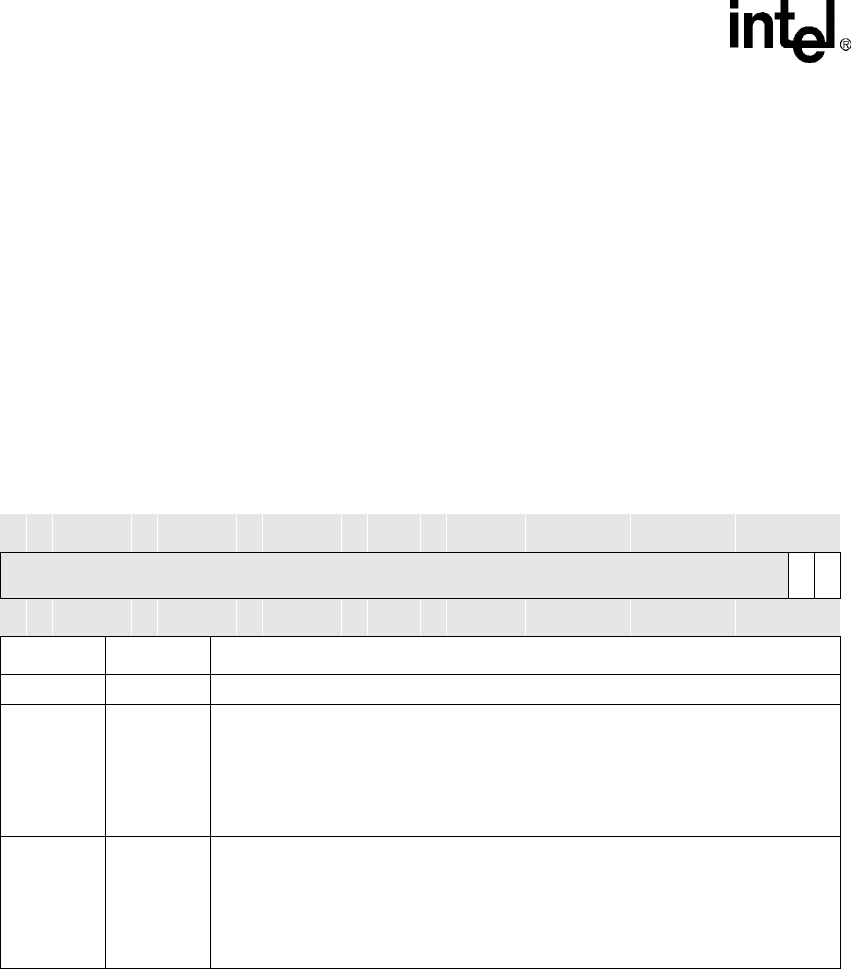

Table 3-22. OSCC Bit Definitions

0x4130_0008 OSCC Clocks and Power Manager

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

reserved

OON

OOK

Reset 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Bits Name Description

[31:2] — reserved

1OON

32.768 KHz OON (write-once only bit)

0 – 32.768 KHz oscillator is disabled. The 3.6864 MHz oscillator (divided by 112) clocks

the RTC and PM.

1 – 32.768 KHz oscillator is enabled. OON can not be cleared once written except by

hardware reset.

Cleared by hardware reset.

0OOK

32.768 kHz OOK (read-only bit)

0 – 32.768 KHz oscillator is disabled or not stable. The 3.6864 MHz oscillator (divided

by 112) clocks the RTC and PM.

1 – 32.768 KHz oscillator has been enabled (OON=1) and stabilized. It will clock the

RTC and PM.

Cleared by hardware reset.