Intel® PXA255 Processor Developer’s Manual 3-29

Clocks and Power Manager

3.5.7 Power Manager Sleep Status Register (PSSR)

The PSSR, shown in Table 3-13, contains the following status flags:

• Software Sleep Status (SSS) flag is set when the sleep mode configuration in the PWRMODE

register is set and sleep mode starts (see Section 3.7.2).

• Battery Fault Status (BFS) bit is set after wake up any time the nBATT_FAULT pin is asserted

(even when the processor is already in sleep mode).

• VDD Fault Status (VFS) bit is set after wake up when the nVDD_FAULT pin is asserted and

causes the processor to enter sleep mode. The VFS bit is not set if software starts the sleep

mode and then the nVDD_FAULT pin is asserted.

• Peripheral Control Hold (PH) bit is set when sleep mode starts and indicates that the GPIO

pins are retaining their sleep mode state values.

• Read Disable Hold (RDH) bit is set in hardware, GPIO, and watchdog resets and sleep mode.

The RDH bit indicates that all the processor’s GPIO input paths are disabled. To allow a GPIO

input pin to be enabled, software must reset the RDH bit by writing a one to it. Clearing RDH

also disables the 10 K to 60 K GPIO pullup resistors that are present during and after

hardware, GPIO and watchdog reset. Sleep mode disables the GPIO input path, but the pullup

resisters are not re-enabled in this case.

To clear a status flag write a 1 to it. Writing a 0 to a status bit has no effect. Hardware, watchdog,

and GPIO resets clear or set the PSSR bits.

This is a read/write register. Ignore reads from reserved bits. Write zeros to reserved bits.

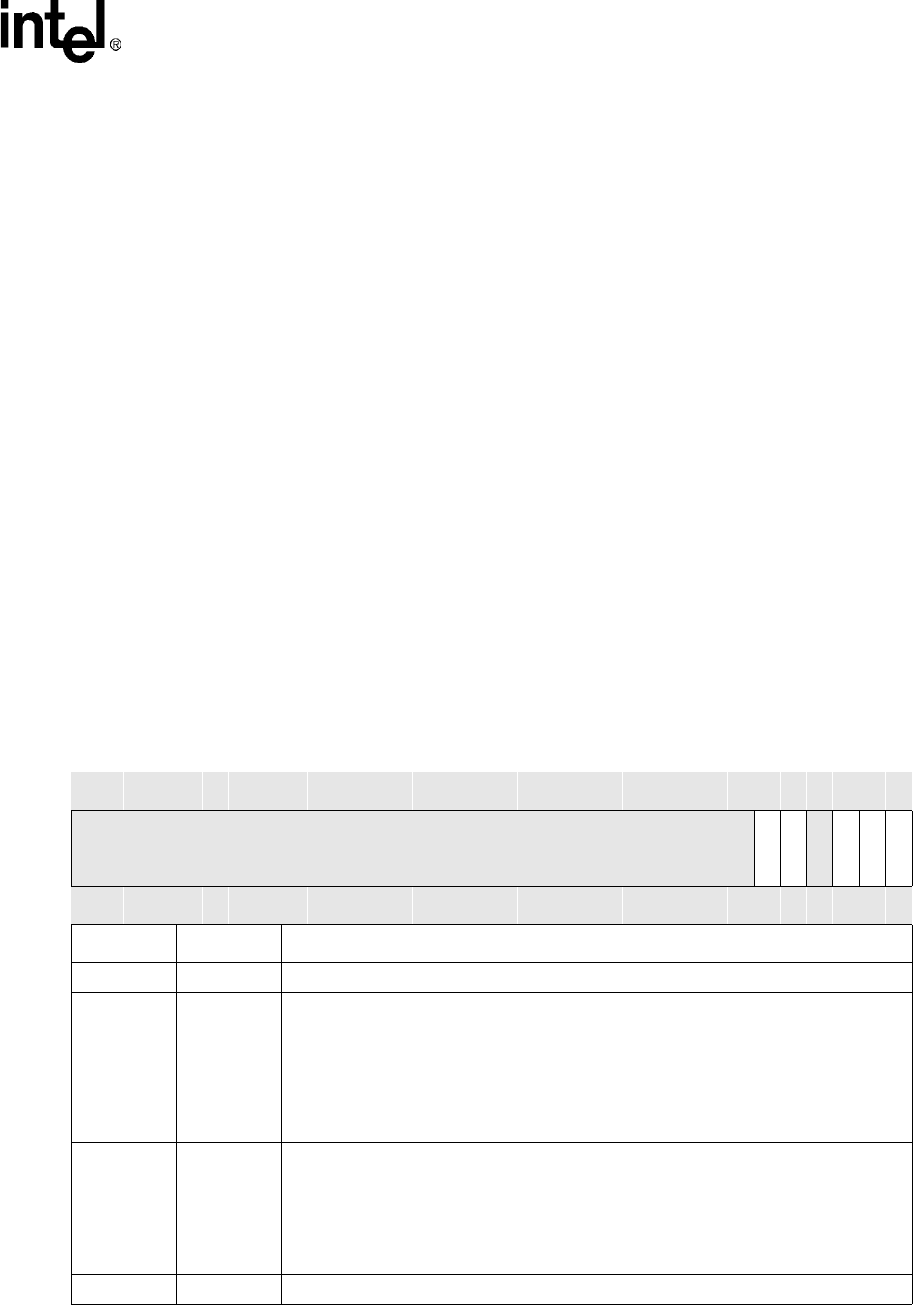

Table 3-13. PSSR Bit Definitions (Sheet 1 of 2)

0x40F0_0004 PSSR Clocks and Power Manager

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

reserved

RDH

PH

reserved

VFS

BFS

SSS

Reset 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0

Bits Name Description

[31:6] — reserved

5RDH

Read Disable Hold.

0 – GPIO pins are configured according to their GPIO configuration

1 – Receivers of all GPIO pins that can act as inputs are disabled and following a

hardware, GPIO, or watchdog reset, internal GPIO pull-ups are active. Must be

cleared by the processor after the peripheral and GPIO interfaces are configured

but before they are used.

Set by hardware, watchdog, and GPIO resets and sleep mode. Cleared by writing a 1.

4PH

Peripheral Control Hold.

0 – GPIO pins are configured according to their GPIO configuration

1 – GPIO pins are being held in their sleep mode state. Set when sleep mode starts.

Must be cleared by the processor after the peripheral interfaces have been

configured but before they are actually used by the processor.

Cleared by hardware, watchdog, and GPIO resets. Cleared by writing a 1.

3—reserved