9-12 Intel® PXA255 Processor Developer’s Manual

I

2

C Bus Interface Unit

9.4.5 Master Operations

When software initiates a read or write on the I

2

C bus, the I

2

C unit transitions from the default

slave-receive mode to master-transmit mode. The 7-bit slave address and the R/nW bit follow the

start pulse. After the master receives an acknowledge, the I

2

C unit enters one of two master modes:

• Master-Transmit — I

2

C unit writes data

• Master-Receive — I

2

C unit reads data

The CPU writes to the ICR register to initiate a master transaction. Data is read and written from

the I

2

C unit through the memory-mapped registers. Table 9-5 describes the I

2

C unit’s

responsibilities as a master device.

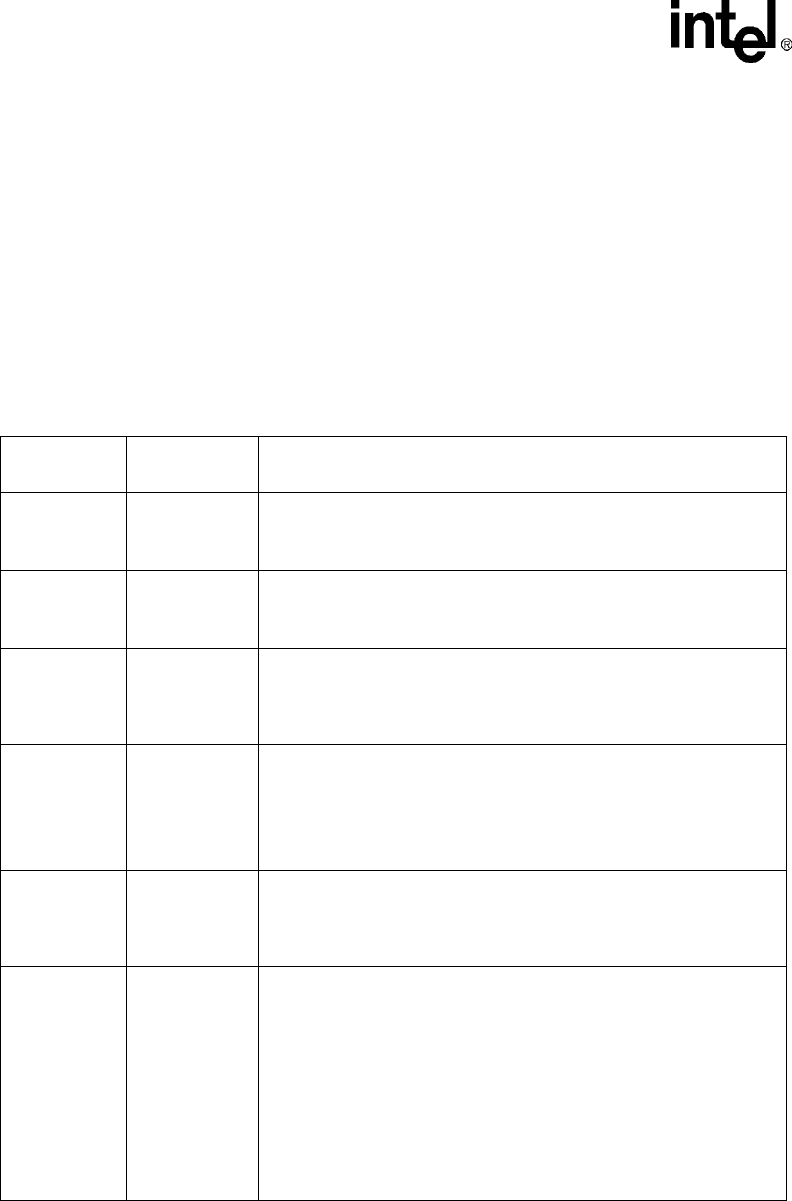

Table 9-5. Master Transactions (Sheet 1 of 2)

I

2

C Master

Action

Mode of

Operation

Definition

Generate clock

output

Master-transmit

Master-receive

• Master drives the SCL line.

• ICR[SCLE] bit must be set.

• ICR[IUE] bit must be set.

Write target

slave address

to IDBR

Master-transmit

Master-receive

•CPU

writes to IDBR bits 7-1 before a START condition enabled.

• First seven bits sent on bus after START.

• See Section 9.3.3.

Write R/nW Bit

to IDBR

Master-transmit

Master-receive

• CPU writes to least significant IDBR bit with target slave address.

• If low, master remains a master-transmitter. If high, master

transitions to a master-receiver.

• See Section 9.4.2.

Signal START

Condition

Master-transmit

Master-receive

• See “Generate clock output” above.

• Performed after target slave address and R/nW bit are in IDBR.

• Software sets ICR[START] bit.

• Software sets ICR[TB] bit to initiate start condition.

• See Section 9.3.3.

Initiate first

data byte

transfer

Master-transmit

Master-receive

• CPU writes byte to IDBR

•I

2

C unit transmits byte when ICR[TB] bit is set.

•I

2

C unit clears ICR[TB] bit and sets ISR[ITE] bit when transfer is

complete.

Arbitrate for

I

2

C Bus

Master-transmit

Master-receive

• If two or more masters signal a start within the same clock period,

arbitration must occur.

•I

2

C unit arbitrates for as long as needed. Arbitration takes place

during slave address and R/nW bit or data transmission and

continues until all but one master loses the bus. No data lost.

• If I

2

C unit loses arbitration, it sets ISR[ALD] bit after byte transfer is

completed and transitions to slave-receive mode.

• If I

2

C unit loses arbitration as it attempts to send target address byte,

I

2

C unit attempts to resend it when the bus becomes free.

• System designer must ensure boundary conditions described in

Section 9.4 do not occur.