3-6 Intel® PXA255 Processor Developer’s Manual

Clocks and Power Manager

3.3.6 Clock Gating

The Clocks Manager contains the CKEN register. This register contains configuration bits that can

disable the clocks to individual units. The configuration bits are used when a module is not being

used. After Hardware Reset, any module that is not being used must have its clock disabled. If a

module is temporarily quiescent but does not have clock gating functionality, the CKEN register

can be used to disable the unit’s clock.

When a module’s clock is disabled, the registers in that module are still readable and writable. The

AC97 is an exception and is completely inaccessible if the clock is disabled.

3.4 Resets and Power Modes

The Clocks and Power Manager Unit determines the processor’s Resets, Power Sequences and

Power Modes. Each behaves differently during operation and has specific entry and exit sequences.

The resets and power modes are:

• Hardware Reset

• Watchdog Reset

• GPIO Reset

• Run Mode

• Turbo Mode

• Idle Mode

• Frequency Change Sequence

• Sleep Mode

3.4.1 Hardware Reset

To invoke the Hardware Reset and reset all units in the processor to a known state, assert the

nRESET pin. Hardware Reset is only intended to be used for power up and complete resets.

3.4.1.1 Invoking Hardware Reset

Hardware Reset is invoked when the nRESET pin is pulled low by an external source. The

processor does not provide a method of masking or disabling the propagation of the external pin

value. When the nRESET pin is asserted, Hardware Reset is invoked, regardless of the mode of

operation. The nRESET_OUT pin is asserted when the nRESET pin is asserted. To enter Hardware

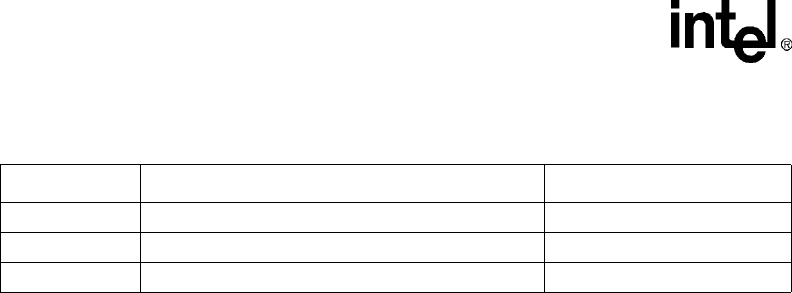

Table 3-3. 147.46 MHz Peripheral PLL Output Frequencies for 3.6864 MHz Crystal

Unit Name Nominal Frequency Actual Frequency

UARTs 14.746 MHz 14.746 MHz

AC97 12.288 MHz 12.288 MHz

I

2

S 146.76 MHz 147.46 MHz