16-22 Intel® PXA255 Processor Developer’s Manual

Network SSP Serial Port

16.5.3 SSP Programmable Serial Protocol Register (SSPSP)

SSPSPx, shown in Table 16-5, contains bit fields used to program the various programmable serial-

protocol parameters. The contents of these registers are ignored if the PSP is not selected.

These are read/write registers. Ignore reads from reserved bits. Write zeros to reserved bits.

25 SCLKDIR

SSP SERIAL BIT RATE CLOCK DIRECTION:

Determines whether the port is the master or slave (with respect to driving SSPSCLK).

0 – Master mode, the port generates SSPSCLK internally, acts as the master, and drives

SSPSCLK.

1 – Slave mode, the port acts as a slave, receives SSPSCLK from an external device and

uses it to determine when to drive transmit data on SSPTXD and when to sample

Receive data on SSPRXD.

24 SFRMDIR

SSP FRAME DIRECTION:

Determines whether the SSP is the master or slave (with respect to driving SSPSFRM.)

When SFRMDIR is set, the port acts as the slave and receives the SSPSFRM signal from an

external device. When the port is configured as a slave to the frame, the external device

driving frame must wait at least the equivalent of 10 SSPSCLKS after enabling the port

before asserting frame. (No external clock cycles are needed, the external device just needs

to wait a certain amount of time before asserting frame).

NOTE: When the GPIO alternate function is selected for the port, this bit has precedence

over the GPIO direction bit. For example, the GPIO pin is an input if SFRMDIR=1.

Alternately, the GPIO pin is an output if SFRMDIR=0.

0 – Master mode, the port generates SSPSFRM internally, acts as the master and drives

SSPSFRM.

1 – Slave mode, the port acts as a slave, receives SSPSFRM from an external device.

23 RWOT

RECEIVE WITH OUT TRANSMIT:

Puts the SSP into a mode similar to half duplex. This allows the port to receive data without

transmitting data (half-duplex only).

When RWOT is set, the port continues to clock in receive data, regardless of data existing in

the transmit FIFO. Data is sent/received immediately after the port enable bit (SSCR0[SSE])

is set. In this mode, if there is no data to send, the DMA service requests and interrupts for

the transmit FIFO must be disabled (clear TSRE and TIE). If the transmit FIFO is empty, all

zeroes are transmitted which must be discarded by the external peripheral.

The transmit FIFO underrun condition does not occur when RWOT is set.

When RWOT is

enabled, SSSR[BUSY] remains active (set to 1) until software clears the RWOT bit.

0 – Transmit/Receive mode.

1 – Receive With Out Transmit mode.

22 — reserved

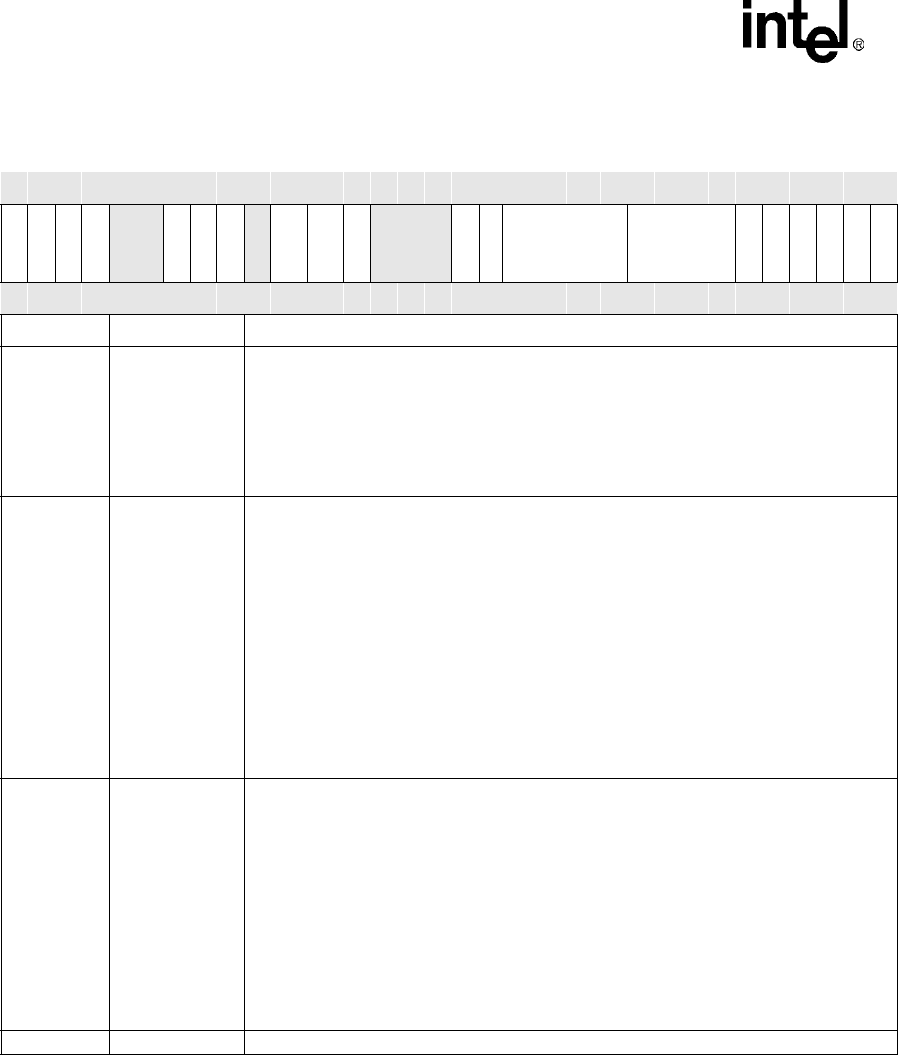

Table 16-4. SSCR1 Bit Definitions (Sheet 2 of 2)

0x04140_0004 SSCR1 Network SSP Serial Port

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

TTELP

TTE

EBCEI

SCFR

reserved

SCLKDIR

SFRMDIR

RWOT

reserved

TSRE

RSRE

TINTE

reserved

STRF

EFWR

RFT TFT

MWDS

SPH

SPO

LBM

TIE

RIE

Reset 0 0 0 0 ? ? 0 0 0 0 0 0 0 ? ? ? 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Bits Name Description