4-42 Intel® PXA255 Processor Developer’s Manual

System Integration Unit

4.5.2.3 PWM Period Control Register (PWM_PERVALn)

The PWM_PERVALn, shown in Table 4-48, contains a 10 bit field called PV. This field determines

the period of the PWM_OUTn waveform in terms of the PSCLK_PWMn clock. If this field is

cleared to zero PWMn is effectively turned off and PWM_OUTn remains in a high state. For any

non-zero value written to the PV field, the output frequency of PWMn is the frequency of the

PSCLK_OUTn divided by the value of (PV + 1). The range of the clock gate extends from a pass-

through of the PSCLK_PWMn to a clock delay of 2

6

or 64 input clocks per output pulse.

When the value of the 10 bit up-counter equals the value of (PV +1), the up-counter and the flip-

flop are reset and the values of PWM_CTRLn, PWM_PERVALn and PWM_DUTYn are loaded

into the internal versions of these registers. Resetting this flip-flop causes PWM_OUTn to go low

and the PWM cycle to start again.

Writing all zeroes to this register results in the output maintaining a high state unless

FDCYCLE=0x0 and DCYCLE=0x0. If FDCYCLE=0x0 and DCYCLE=0x0, the output maintains

a low state regardless of the value in the PV bit field.

Note: Due to internal timing requirements, all changes to any of the PWM registers must be complete a

minimum of 4 core clock cycles before the start of end of a PWM clock cycle in order to guarantee

that the following PWM cycle implements the new values.

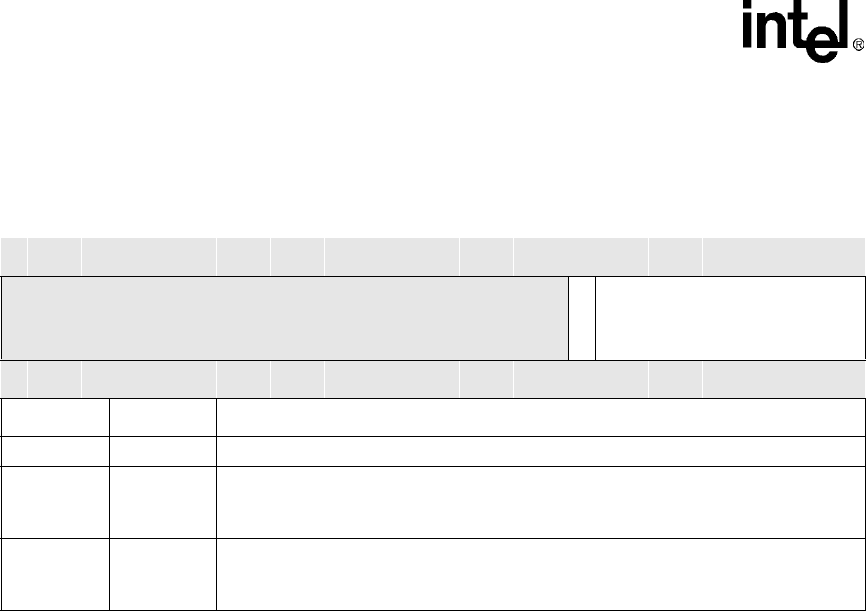

Table 4-47. PWM_DUTYn Bit Definitions

Physical Address

0x40B0_0004

0x40C0_0004

PWM Duty Cycle Registers

(PWM_DUTY0, PWM_DUTY1)

System Integration Unit

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

reserved

FDCYCLE

DCYCLE

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Bits Name Description

<31:11> — reserved

<10> FDCYCLE

PWMn Full Duty Cycle

0 – PWM clock (PWM_OUTn) duty cycle is determined by DCYCLE field.

1 – PWM_OUTn is set high and does not toggle.

<9:0> DCYCLE

PWMn Duty Cycle

Duty cycle of PWMn clock, i.e. the number of PSCLK_PWM cycles PWMn is asserted

within one cycle of PWMn.