13-10 Intel® PXA255 Processor Developer’s Manual

AC’97 Controller Unit

CODEC Ready, sent by the CODEC on its data out stream in bit 15 of Slot 0, is not expected to

change during normal operation. The AC’97 Specification revision 2.0 requires that a CODEC

only change its CODEC Ready status in response to a power down (PR) state change issued by the

ACUNIT. The ACUNIT’s hardware by itself does not monitor the CODEC Ready for the purpose

of sending or receiving data. The ACUNIT stores CODEC Ready in the PCR bit of the GSR for a

primary CODEC and SCR bit of the GSR for a secondary CODEC. Software should monitor PCR

or SCR to trigger a DMA or a programmed I/O operation. The ACUNIT only samples CODEC

Ready valid once and then ignores it for subsequent frames. CODEC Ready is only resampled after

a PR state change.

13.4.2.2 Slot 1: Status Address Port/SLOTREQ bits

Slot 1 is the Status Address Port. Slot 1 monitors the status of ACUNIT functions including, but

not limited to, mixer settings and power management.

Slot 1 echoes the control register index for the data to be returned in Slot 2, if the ACUNIT tags

Slot 1 and Slot 2 as valid during Slot 0.

The ACUNIT only accepts status data (Slot 2 of incoming stream) if the accompanying control

register index (Slot 1 of incoming stream) matches the last valid control register index that was sent

in Slot 1 of the outgoing stream of the most recent previous frame.

For multiple sample rate output, the CODEC examines its sample-rate control registers, its FIFOs’

states, and the incoming SDATA_OUT tag bits at the beginning of each audio output frame to

determine which SLOTREQ bits to set active (low). SLOTREQ bits asserted during the current

audio input frame indicate which output slots require data from the ACUNIT in the next audio

output frame. For fixed 48 kHz operation, the SLOTREQ bits are set active (low), and a sample is

transferred during each frame.

For multiple sample-rate input, the tag bit for each input slot indicates whether valid data is

present.

Again, Slot 1 delivers a CODEC control register index and multiple “sample-rate slot request

flags” for all output slots. AC’97 defines the ten least significant bits of Slot 1 as CODEC on-

demand data request flags for outgoing stream Slots 3-12. For two-channel audio, only data-

request flags corresponding to slots 3 and 4 are meaningful.

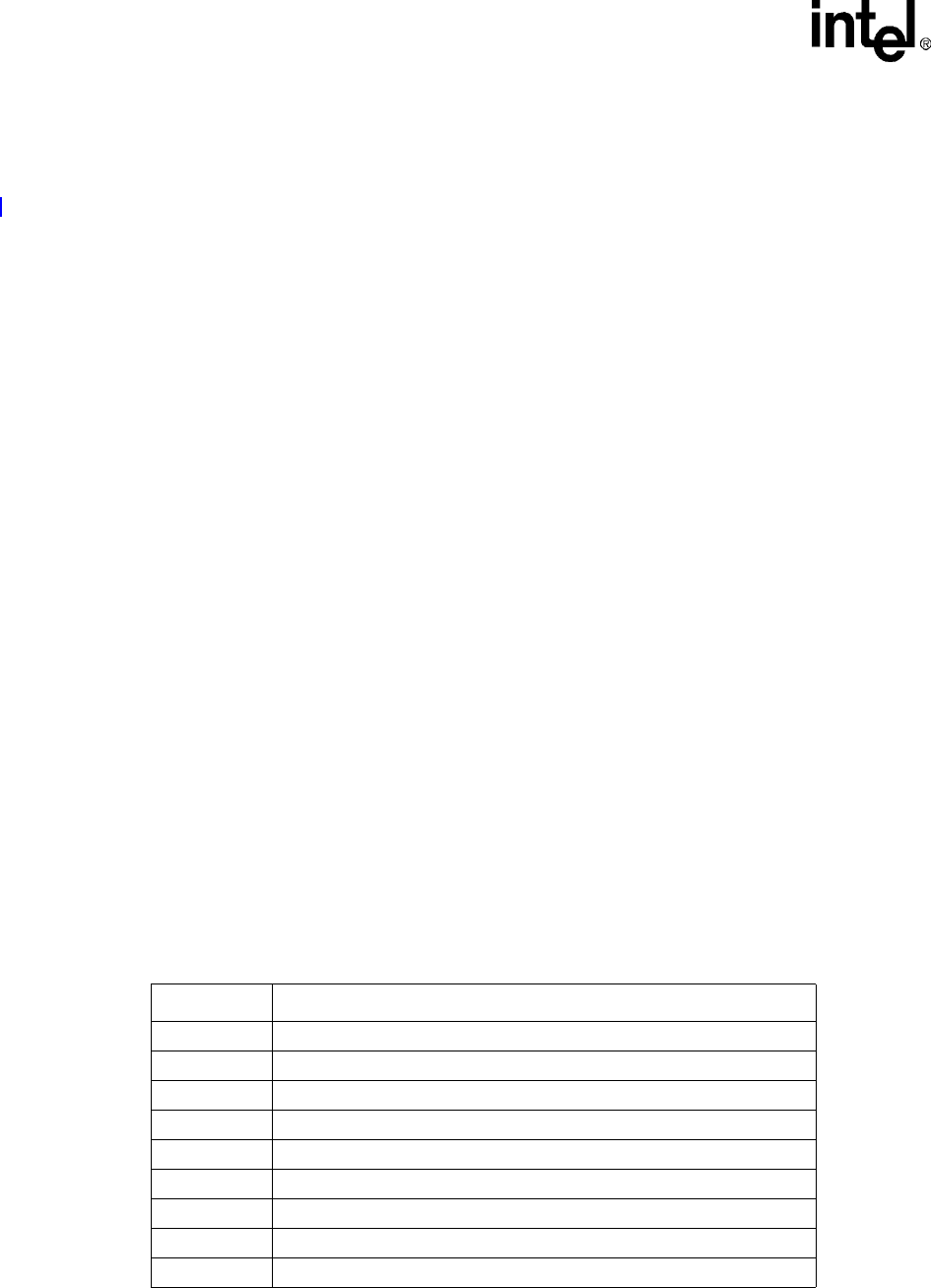

Table 13-5. Input Slot 1 Bit Definitions (Sheet 1 of 2)

Bit Description

19 reserved (Filled with zero)

18-12 Control register Index (Filled with zeroes if AC’97 tags it invalid)

11 Slot 3 request: PCM Left channel

10 Slot 4 request: PCM Right channel

9 Slot 5 request: Modem Line 1

8 Slot 6 request: NA

7 Slot 7 request: NA

6 Slot 8 request: NA

5 Slot 9 request: NA