11-10 Intel® PXA255 Processor Developer’s Manual

Fast Infrared Communication Port

11.3.2 FICP Control Register 1 (ICCR1)

The ICCR1, shown in Table 11-3, contains the 8-bit address match value field that the FICP uses to

selectively receive frames. To allow the address match value to be changed during active receive

operation, ICCR1 may be written while the FICP is enabled.

This is a read/write register. Ignore reads from reserved bits. Write zeros to reserved bits.

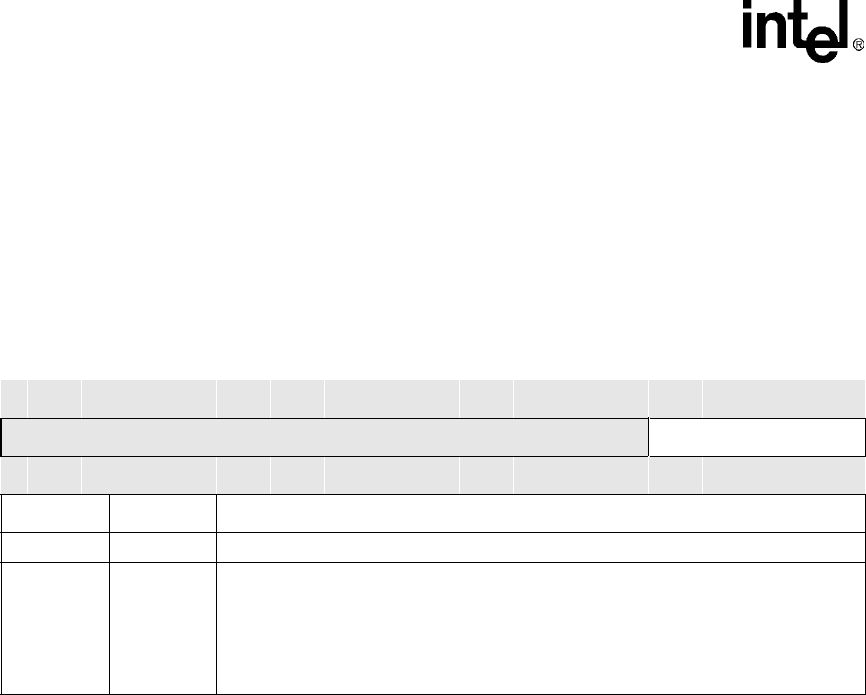

Table 11-3. ICCR1 Bit Definitions

0x4080_0004

Fast Infrared Communication Port

Control Register 1 (ICCR1)

Fast Infrared Communication Port

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

reserved AMV

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Bits Name Description

[31:8] — reserved

[7:0] AMV

Address match value.

The 8-bit value used by receiver logic to compare to address of incoming frames. If AME=1

and AMV matches the address of the incoming frame, store the frame address, control,

and data in receive FIFO. If the address does not match, ignore the frame and search for

the next preamble.

The broadcast address 0xFF in the incoming frame always generates a match.