9-22 Intel® PXA255 Processor Developer’s Manual

I

2

C Bus Interface Unit

When the ICR[UR] bit is set, the I

2

C unit resets but the associated I

2

C MMRs remain intact. When

resetting the I

2

C unit with the ICR’s unit reset, use the following guidelines:

1. Set the reset bit in the ICR register and clear the remainder of the register.

2. Clear the ISR register.

3. Clear reset in the ICR.

9.9 Register Definitions

9.9.1 I

2

C Bus Monitor Register (IBMR)

The IBMR, shown in Table 9-8, tracks the status of the SCL and SDA pins. The values of these

pins are recorded in this read-only IBMR so software can determine when the I

2

C bus is hung and

the I

2

C unit must be reset.

This is a read/write register. Ignore reads from reserved bits. Write zeros to reserved bits.

9.9.2 I

2

C Data Buffer Register (IDBR)

The processor uses the IDBR, shown in Table 9-9, to transmit and receive data from the I

2

C bus.

The IDBR is accessed by the program I/O on one side and by the I

2

C shift register on the other. The

IDBR receives data coming into the I

2

C unit after a full byte is received and acknowledged. The

processor core writes data going out of the I

2

C unit to the IDBR and sends it to the serial bus.

When the I

2

C unit is in transmit mode (master or slave), the processor writes data to the IDBR over

the internal bus. The processor writes data to the IDBR when a master transaction is initiated or

when the IDBR Transmit Empty Interrupt is signalled. Data moves from the IDBR to the shift

register when the Transfer Byte bit is set. The IDBR Transmit Empty Interrupt is signalled (if

enabled) when a byte is transferred on the I

2

C bus and the acknowledge cycle is complete. If the

IDBR is not written by the processor and a STOP condition is not in place before the I

2

C bus is

ready to transfer the next byte packet, the I

2

C unit inserts wait states until the processor writes the

IDBR and sets the Transfer Byte bit.

When the I

2

C unit is in receive mode (master or slave), the processor reads IDBR data over the

internal bus. The processor reads data from the IDBR when the IDBR Receive Full Interrupt is

signalled. The data moves from the shift register to the IDBR when the ACK cycle is complete.

The I

2

C unit inserts wait states until the IDBR is read. Refer to Section 9.4.3 for more information

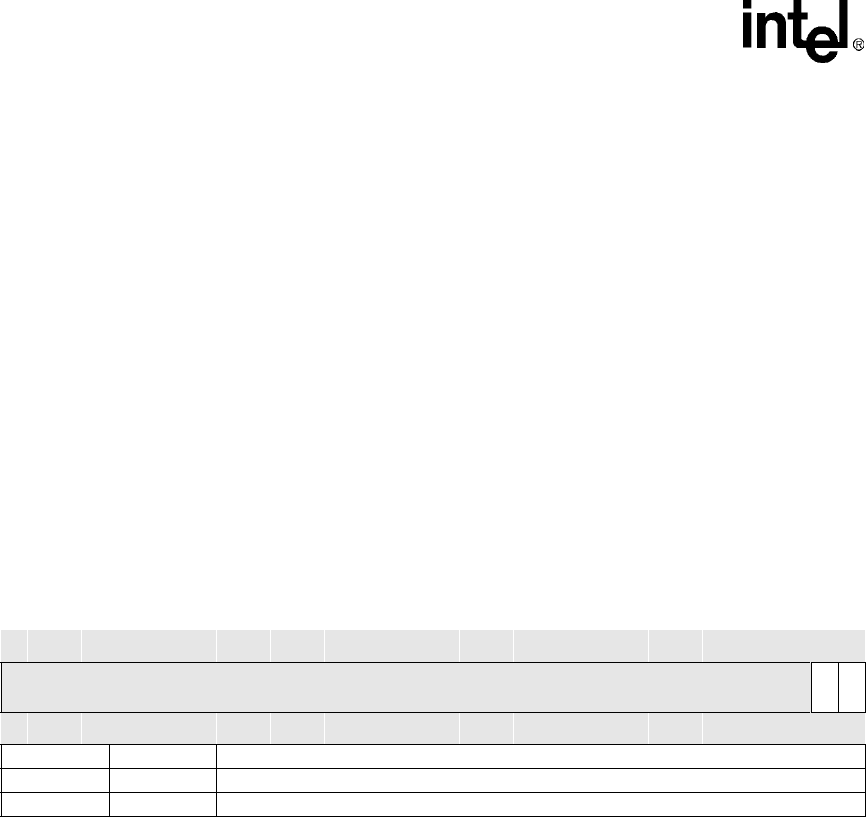

Table 9-8. IBMR Bit Definitions

Physical Address

4030_1680

I

2

C Bus Monitor Register I

2

C Bus Interface Unit

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

reserved

SCLS

SDAS

Reset 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1

31:2 — reserved

1 SCLS SCL Status: This bit continuously reflects the value of the SCL pin.

0 SDAS SDA Status: This bit continuously reflects the value of the SDA pin.