Intel® PXA255 Processor Developer’s Manual 13-11

AC’97 Controller Unit

SLOTREQ bits are independent of the Control Register Index bits.

Note: Slot requests for Slot 3 and Slot 4 are always set or cleared in tandem (both are set or both are

cleared).

13.4.2.3 Slot 2: Status Data Port

Slot 2 delivers 16-bit control register read data.

Note: If Slot 2 is tagged invalid, the CODEC fills the entire slot with zeroes.

13.4.2.4 Slot 3: PCM Record Left Channel

Slot 3 contains the CODEC left channel output.

The CODEC transmits its ADC output data (MSB first) and fills any trailing non-valid bit positions

with zeroes.

13.4.2.5 Slot 4: PCM Record Right Channel

Slot 4 contains the CODEC right-channel output.

The CODEC transmits its ADC output data (MSB first), and fills any trailing non-valid bit

positions with zeroes.

13.4.2.6 Slot 5: Optional Modem Line CODEC

Slot 5 contains MSB justified line modem ADC output data (if the line modem CODEC is

supported).

The ACUNIT only supports a 16-bit ADC output resolution from the optional line modem.

13.4.2.7 Slot 6: Optional Dedicated Microphone Record Data

Slot 6 contains an optional third PCM system-input channel available for dedicated use by a

microphone. This input channel supplements a true stereo output to enable a more precise echo-

cancellation algorithm for speakerphone applications.

4 Slot 10 request: NA

3 Slot 11 request: NA

2 Slot 12 request: NA

1,0 reserved (Filled with zero)

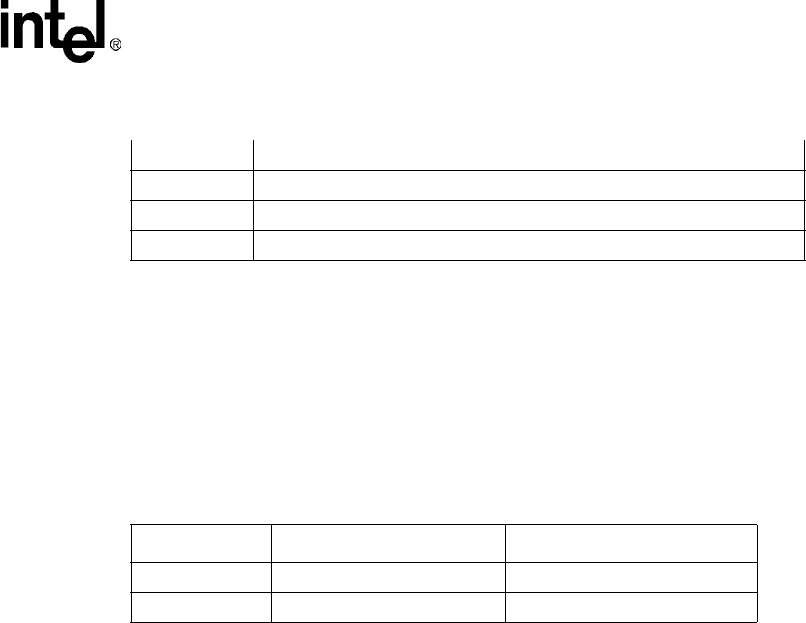

Table 13-5. Input Slot 1 Bit Definitions (Sheet 2 of 2)

Table 13-6. Input Slot 2 Bit Definitions

Bit Name Description

Bit(19:4) Control register read data Filled with data

Bit(3:0) reserved Filled with zeroes