Intel® PXA255 Processor Developer’s Manual 3-33

Clocks and Power Manager

3.5.11 Reset Controller Status Register (RCSR)

The CPU uses the RCSR, shown in Table 3-19, to determine a reset’s last cause or causes. The

processor can be reset in four ways:

• Hardware reset

• Watchdog reset

• Sleep mode

• GPIO reset

Refer to Table 2-4, “Effect of Each Type of Reset on Internal Register State” on page 2-6 for details

of the behavior of different modules during each type of reset.

Each RCSR status bit is set by a different reset source and can be cleared by writing a 1 back to the

bit. The RCSR status bits for watchdog reset, sleep mode, and GPIO resets have a hardware reset

state of zero.

This is a read/write register. Ignore reads from reserved bits. Write zeros to reserved bits.

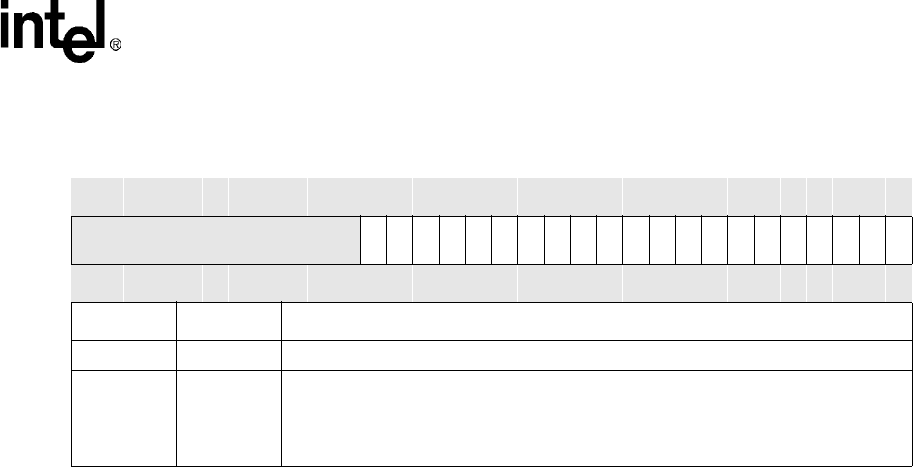

Table 3-18. PGSR2 Bit Definitions

0x40F0_0028 PGSR2 Clocks and Power Manager

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

reserved

SS84

SS83

SS82

SS81

SS80

SS79

SS78

SS77

SS76

SS75

SS74

SS73

SS72

SS71

SS70

SS69

SS68

SS67

SS66

SS65

SS64

Reset 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Bits Name Description

[31:17] — reserved

[16:0] SSx

If programmed as an output, Sleep state of GPx

0 – Pin is driven to a zero during sleep mode

1 – Pin is driven to a one during sleep mode

Cleared by hardware, watchdog, and GPIO resets.