15-24 Intel® PXA255 Processor Developer’s Manual

MultiMediaCard Controller

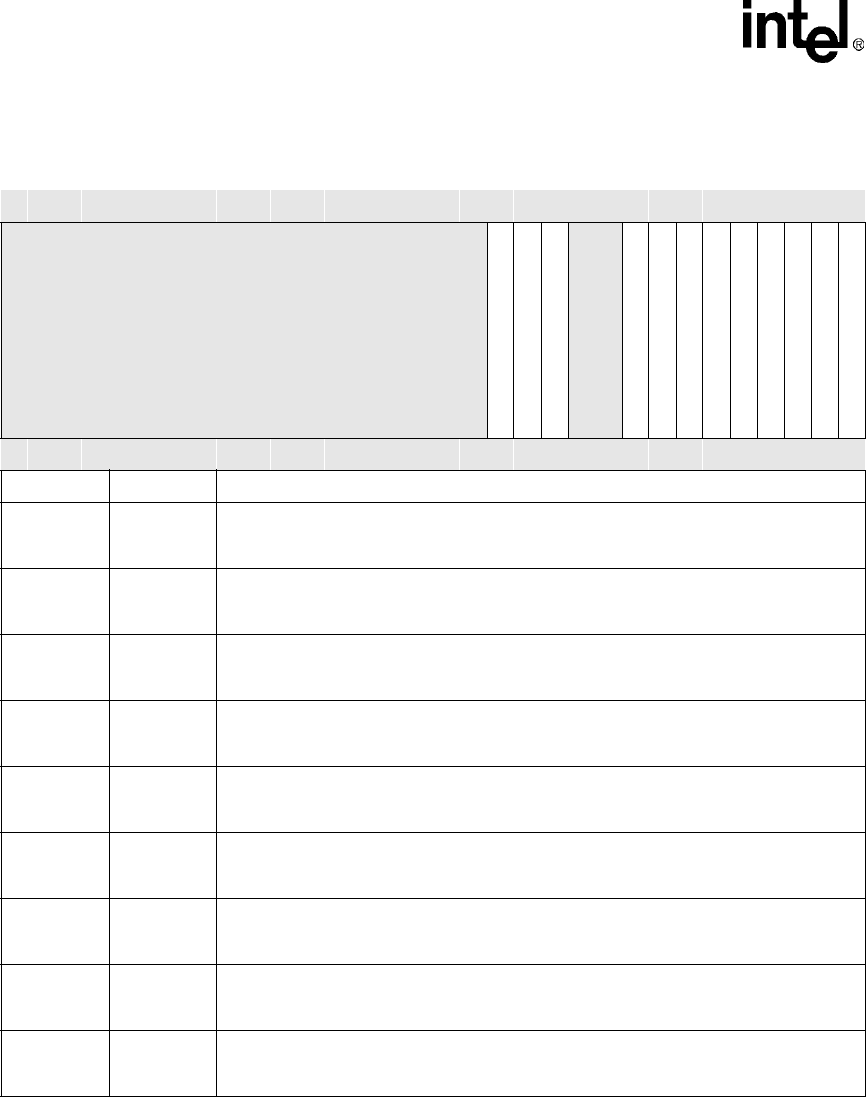

15.5.3 MMC_CLKRT Register (MMC_CLKRT)

MMC_CLKRT, shown in Table 15-7, specifies the frequency division of the MMC bus clock. The

software is responsible for setting this register.

The software can only write this register after the clock is turned off and the software has received

an interrupt that indicates the clock is turned off.

8 CLK_EN

Clock Enabled

0 – MMC clock is off

1 – MMC clock is on

7

RECV_FIFO_

FULL

Receive FIFO Full

0 – Receive FIFO is not full

1 – Receive FIFO is full

6

XMIT_FIFO_E

MPTY

Transmit FIFO Empty

0 – Transmit FIFO is not empty

1 – Transmit FIFO is empty

5

RES_CRC_E

RR

Response CRC Error

0 – No error on the response CRC

1 – CRC error occurred on the response

4

SPI_READ_E

RROR_TOKE

N

SPI Read Error Token

0 – SPI data error token has not been received

1 – SPI data error token has been received

3

CRC_READ_

ERROR

CRC Read Error

0 – No error on received data

1 – CRC error occurred on received data

2

CRC_WRITE_

ERROR

CRC Write Error

0 – No error on transmission of data

1 – Card observed erroneous transmission of data

1

TIME_OUT_R

ESPONSE

Time Out Response

0 – Card response has not timed out

1 – Card response timed out

0

READ_TIME_

OUT

Read Time Out

0 – Card read data has not timed out

1 – Card read data timed out

Table 15-6. MMC_STAT Bit Definitions (Sheet 2 of 2)

Physical Address

0x4110_0004

MMC_STAT Register MultiMediaCard Controller

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

reserved

END_CMD_RES

PRG_DONE

DATA_TRAN_DONE

reserved

CLK_EN

RECV_FIFO_FULL

XMIT_FIFO_EMPTY

RES_CRC_ERR

SPI_READ_ERROR_TOKEN

CRC_READ_ERROR

CRC_WRITE_ERROR

TIME_OUT_RESPONSE

READ_TIME_OUT

Reset 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0

Bits Name Description