Intel® PXA255 Processor Developer’s Manual 3-31

Clocks and Power Manager

3.5.9 Power Manager Fast Sleep Walk-up Configuration Register

(PMFW)

The PSPR, shown in Table 3-15, provides a single bit called FWAKE which is used to select

between the standard and fast sleep walk-up sequences. The PMFW register is reset by a hardware

reset, GPIO reset, watchdog reset, but is not cleared by the sleep walk-up sequence. Using an

exception handler to invoke sleep in response to a power fault event is advantageous because

software can clear the PMFW[FWAKE] bit and configure the power management IC to use

PWR_EN to disable the core power supply during sleep to minimize power consumption from a

critically low battery. Also, the PCFR[OPDE] bit must be cleared to enable the 3.6864 MHz

oscillator during sleep when fast sleep walk-up is selected by setting the PMFW[FWAKE] bit.

This is a read/write register. Ignore reads from reserved bits. Write zeros to reserved bits.

3.5.10 Power Manager GPIO Sleep State Registers (PGSR0,

PGSR1, PGSR2)

PGSR0, PGSR1, and PGSR2, shown in Table 3-16, Table 3-17, and Table 3-18 allow software to

select the output state of each GPIO pin when the processor goes into sleep mode. When a

transition to sleep mode is required (through software or the nBATT_FAULT or nVDD_FAULT

pin), the contents of the PGSR registers are loaded into the GPIO output data registers that software

normally controls through the GPSR and GPCR registers. Only pins that are already configured as

outputs reflect the new state. All bits in the output registers are loaded. When the processor re-

enters the run mode, these GPIO pins retain the programmed sleep state until software resets

PSSR[PH]. If a pin is reconfigured from an input to an output, the register’s last contents are driven

onto the pin.

This is a read/write register. Ignore reads from reserved bits. Write zeros to reserved bits.

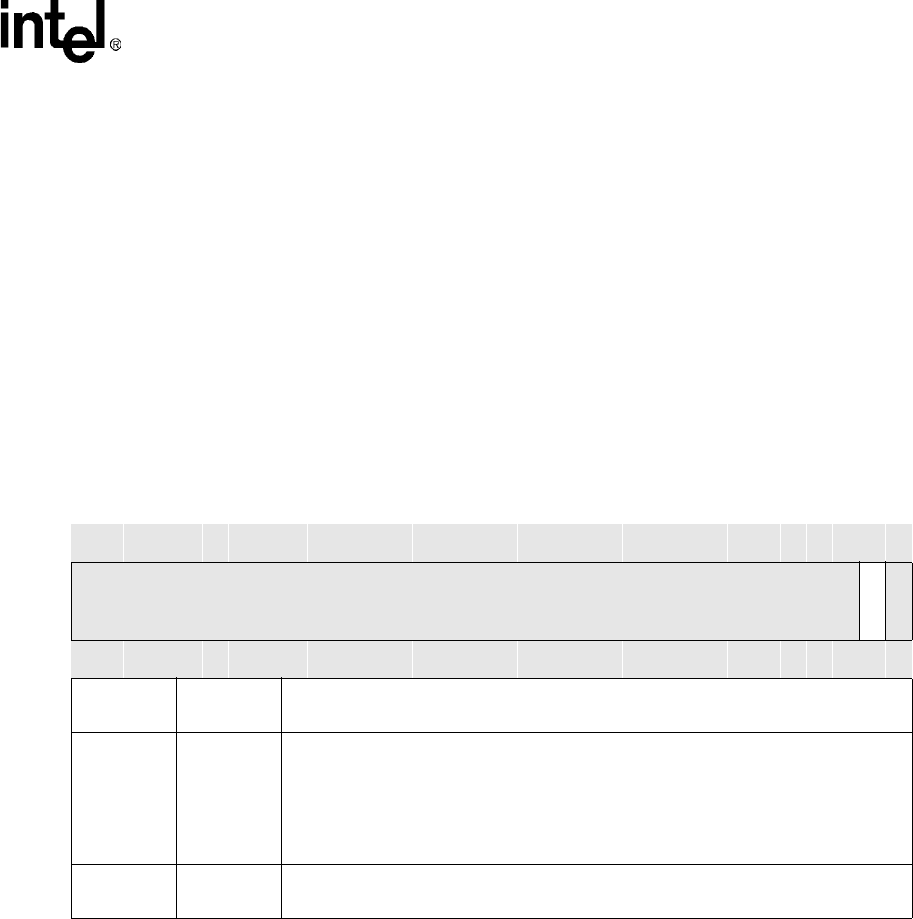

Table 3-15. PMFW Register Bitmap and Bit Definitions

0x40F0 0034

Power Manager Fast Sleep Wakeup

Configuration Register (PMFW)

Power Manager

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Reserved

FWAKE

Reserved

Reset 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

[31:3] —

Reserved

Read undefined and must always be written with zeroes.

[1] FWAKE

FAST WAKEUP ENABLE

0 – Selects the standard sleep wakeup sequence with a 10 ms power supply

stabilization delay when power is disabled during sleep.

1 – Selects the fast sleep wakeup sequence without a power supply stabilization delay

when power is maintained during sleep.

Cleared by hardware reset.

[0] —

Reserved

Read undefined and must always be written with zeroes.