4-24 Intel® PXA255 Processor Developer’s Manual

System Integration Unit

4.2.2.4 Interrupt Controller IRQ Pending Register (ICIP) and FIQ Pending

Register (ICFP)

The ICIP and the ICFP, shown in Table 4-33 and Table 4-34, contain one bit per interrupt (22 total.)

These bits indicate an interrupt request has been made by a unit. Inside the interrupt service

routine, read the ICIP and ICFP to determine the interrupt source. In general, software then reads

status registers within the interrupting device to determine how to service the interrupt. Bits within

the ICPR (see Section 4.2.2.5) are read only, and represent the logical OR of the status bits in the

ICIP and ICFP for a given interrupt. Once an interrupt has been serviced, the handler writes a one

to the required status bit, clearing the pending interrupt at the source.

Clearing the interrupt status bit at the source, automatically clears the corresponding ICIP or ICFP

flag, provided there are no other interrupt status bits set within the source unit.

Table 4-36 describes the available first-level interrupts and their location in the ICPR.

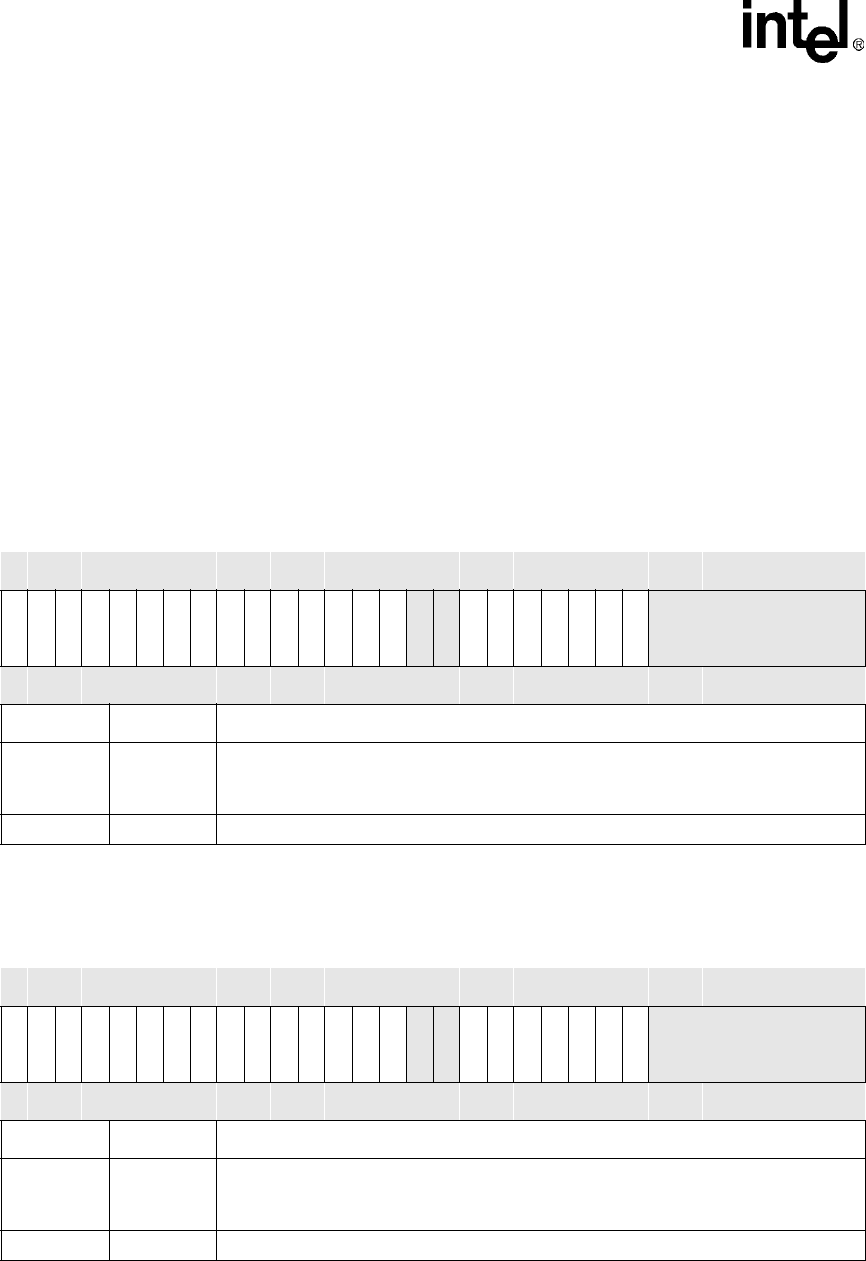

Table 4-33. ICIP Bit Definitions

Physical Address

0x40D0_0000

ICIP System Integration Unit

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

IP31

IP30

IP29

IP28

IP27

IP26

IP25

IP24

IP23

IP22

IP21

IP20

IP19

IP18

IP17

reserved

reserved

IP14

IP13

IP12

IP11

IP10

IP9

IP8

reserved

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 ? ? ? ? ? ? ? ?

Bits Name Description

<31:8> IP[x]

IRQ Pending x (where x = 8 through 14 and 17 through 31).

0 – IRQ NOT requested by any enabled source.

1 – IRQ requested by an enabled source.

<7:0> — reserved

Table 4-34. ICFP Bit Definitions

Physical Address

0x40D0_000C

ICFP System Integration Unit

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

FP31

FP30

FP29

FP28

FP27

FP26

FP25

FP24

FP23

FP22

FP21

FP20

FP19

FP18

FP17

reserved

reserved

FP14

FP13

FP12

FP11

FP10

FP9

FP8

reserved

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 ? ? ? ? ? ? ? ?

Bits Name Description

<31:8> FP[x]

FIQ Pending x (where x = 8 through 14 and 17 through 31).

0 – FIQ NOT requested by any enabled source.

1 – FIQ requested by an enabled source.

<7:0> — reserved