13-30 Intel® PXA255 Processor Developer’s Manual

AC’97 Controller Unit

13.8.3.14 Modem-Out Status Register (MOSR)

This is a read/write register. Ignore reads from reserved bits. Write zeros to reserved bits.

13.8.3.15 Modem-In Status Register (MISR)

This is a read/write register. Ignore reads from reserved bits. Write zeros to reserved bits.

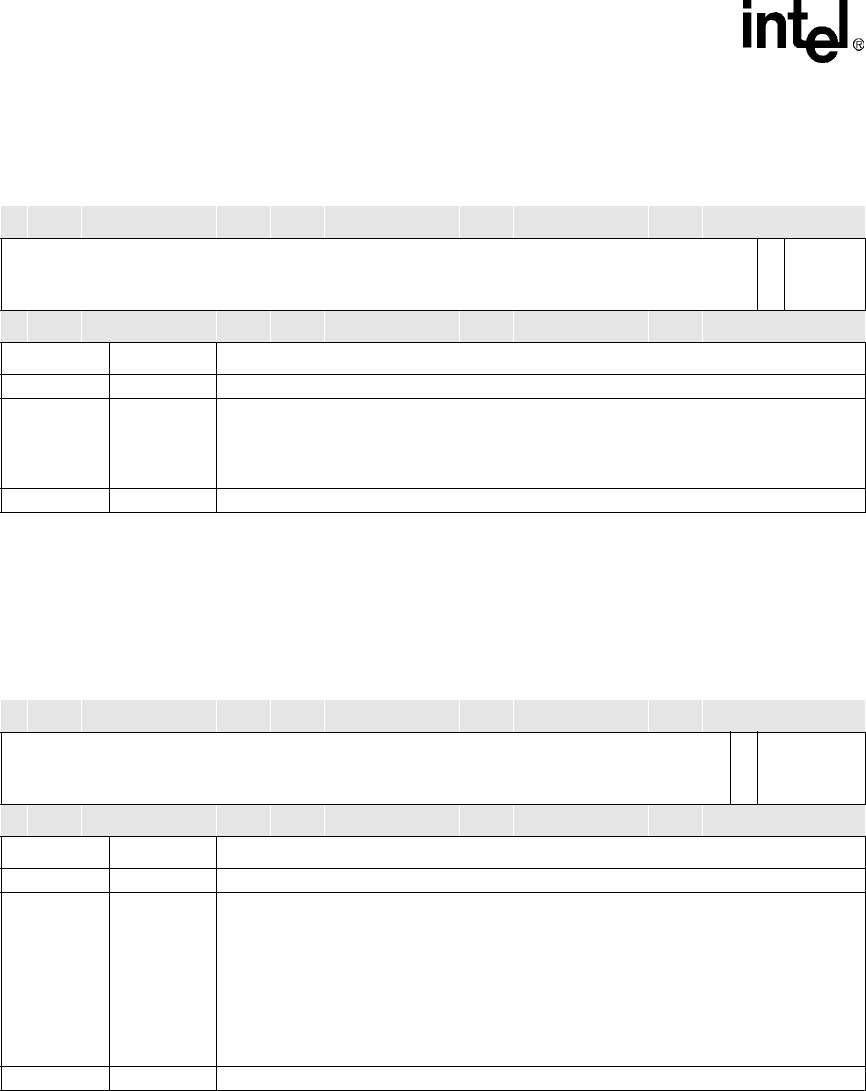

Table 13-19. MICR Bit Definitions

Physical Address

4050_0108

MICR Register AC’97 Controller Unit

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

reserved

FEIE

reserved

Reset 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Bits Name Description

31:4 — reserved

3FEIE

FIFO Error Interrupt Enable (FEIE)

Controls whether a receive FIFO error causes an interrupt.

0 = No interrupt will occur even if bit 4 in the MISR is set

1 = An interrupt will occur if bit 4 in the MISR is set.

2:0 — reserved

Table 13-20. MOSR Bit Definitions

Physical Address

4050_0110

MOSR Register AC’97 Controller Unit

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

reserved

FIFOE

reserved

Reset 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Bits Name Description

31:5 — reserved

4FIFOE

FIFO error (FIFOE)

0 = No transmit FIFO errors have occurred

1 = A transmit FIFO error occurred. This bit is set if a transmit FIFO underrun occurs. In

this case, the last valid sample is repetitively sent out and the pointers are not

incremented.This could happen due to:

c. No more valid buffer data available for transmits.

d. Buffer data available but DMA controller has excessive bandwidth requirements.

Bit is cleared by writing a 1 to this bit position.

3:0 — reserved