13-26 Intel® PXA255 Processor Developer’s Manual

AC’97 Controller Unit

13.8.3.7 CODEC Access Register (CAR)

This is a read/write register. Ignore reads from reserved bits. Write zeros to reserved bits.

13.8.3.8 PCM Data Register (PCDR)

This is a read/write register. Ignore reads from reserved bits. Write zeros to reserved bits.

Writing a 32-bit sample to this register updates the data into the PCM Transmit FIFO. Reading this

register gets a 32-bit sample from the PCM Receive FIFO.

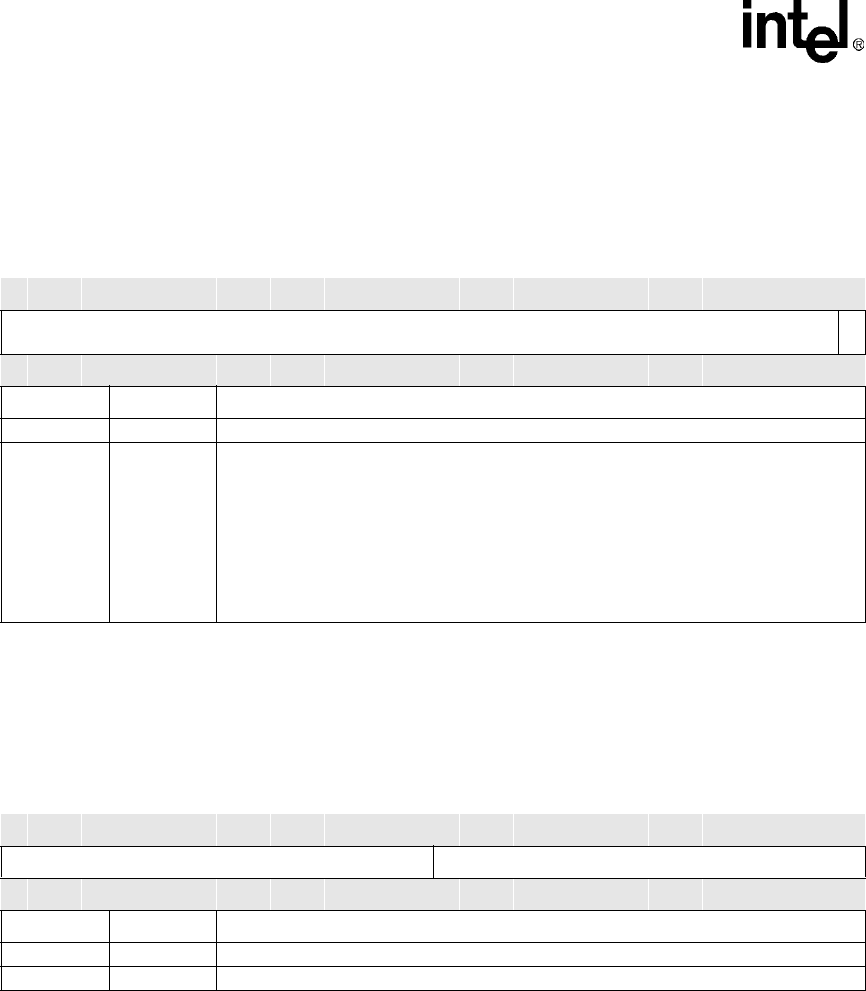

Table 13-13. CAR Bit Definitions

Physical Address

4050_0020

CAR Register AC’97 Controller Unit

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

reserved

CAIP

Reset 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Bits Name Description

31:1 — reserved

0CAIP

CODEC Access In Progress (CAIP)

This bit is read by software to check whether a CODEC IO cycle is currently in progress.

0 = No cycle is in progress and the act of reading the register sets this bit to ‘1’. This

reserves the right for the software driver to perform the IO cycle. Once the cycle is

complete, this bit is automatically cleared. Software can clear this bit by writing a ‘0’ to

this bit location if it decides not to perform a CODEC IO cycle after having read this bit.

1 = Indicates that another driver is performing a CODEC IO cycle across the AC-link and

the currently accessing driver must try again later. (This bit applies to all CODEC IO

cycles - GPIO or otherwise).

Table 13-14. PCDR Bit Definitions

Physical Address

4050_0040

PCDR Register AC’97 Controller Unit

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

PCM_RDATA PCM_LDATA

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Bits Name Description

31:16 PCM_RDATA PCM right-channel data

15:0 PCM_LDATA PCM left-channel data