16-20 Intel® PXA255 Processor Developer’s Manual

Network SSP Serial Port

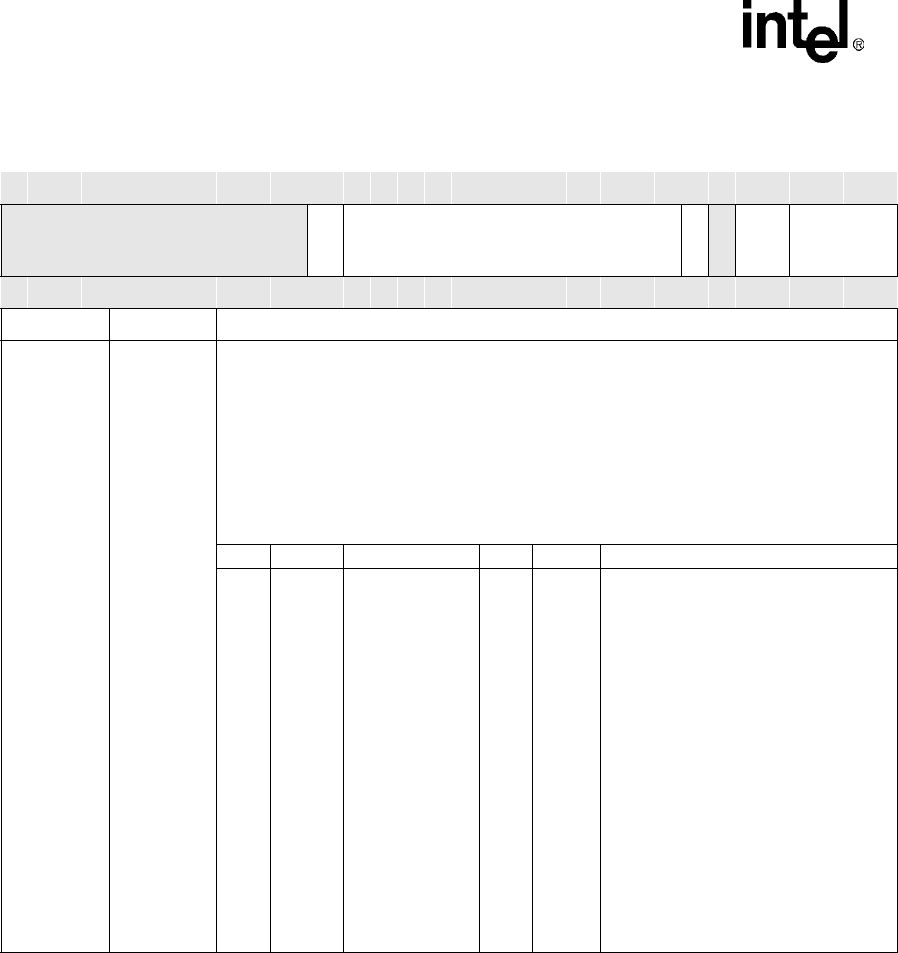

16.5.2 SSP Control Register 1 (SSCR1)

SSCR1, shown in Table 16-4, contains bit fields that control various SSP functions. Before

enabling the port (using SSCR0[SSE]), the desired values for this register must be set.

These are read/write registers. Ignore reads from reserved bits. Write zeros to reserved bits.

3:0 DSS

DATA SIZE SELECT:

Used in conjunction with EDSS to select the size of the data transmitted and received by the

SSP. The concatenated 5-bit value of EDSS and DSS provides a data range from four to 32-bits

in length.

For the Microwire* protocol, DSS and EDSS are used to determine the receive data size. The

size of the transmitted data is either eight or 16-bits (determined by SSCR1[MWDS]) and the

EDSS bit is ignored. The EDSS and DSS fields are ignored for Microwire* transmit data size -

MWDS (alone) configures this. However, for all modes (including Microwire*) EDSS and DSS

are used to determine the receive data size.

When data is programmed to be less than 32 bits, the FIFO must be programmed right-justified.

EDSS DSS Data Size EDSS DSS Data Size

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0b0000

0b0001

0b0010

0b0011

0b0100

0b0101

0b0110

0b0111

0b1000

0b1001

0b1010

0b1011

0b1100

0b1101

0b1110

0b1111

17-bit data

18-bit data

19-bit data

20-bit data

21-bit data

22-bit data

23-bit data

24-bit data

25-bit data

26-bit data

27-bit data

28-bit data

29-bit data

30-bit data

31-bit data

32-bit data

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0b0000

0b0001

0b0010

0b0011

0b0100

0b0101

0b0110

0b0111

0b1000

0b1001

0b1010

0b1011

0b1100

0b1101

0b1110

0b1111

reserved, undefined

reserved, undefined

reserved, undefined

4-bit data

5-bit data

6-bit data

7-bit data

8-bit data

9-bit data

10-bit data

11-bit data

12-bit data

13-bit data

14-bit data

15-bit data

16-bit data

Table 16-3. SSCR0 Bit Definitions (Sheet 2 of 2)

0x4140_0000 SSCR0 Network SSP Serial Port

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

reserved

EDSS

SCR

SSE

reserved

FRF

DSS

? ? ? ? ? ? ? ? ? ? ? 0 0 0 0 0 0 0 0 0 0 0 0 0 0 ? 0 0 0 0 0 0

Bits Name Description