Intel® PXA255 Processor Developer’s Manual 8-11

Synchronous Serial Port Controller

8.7.1.5 Serial Clock Rate (SCR)

The 8-bit serial clock rate (SCR) bit-field is used to select the SSPC bit rate. The SSPC has 256 bit

rates, from 7.2 Kbps to 1.8432 Mbps. The serial clock generator uses the internal 3.6864 MHz

clock or an external clock provided through SSPEXTCLK. The clock is divided by 2, then divided

by the programmable SCR value (0 to 255) plus 1 to generate the serial clock (SSPSCLK). The

resultant clock is driven on the SSPSCLK pin and is used by the SSP’s transmit logic to drive data

on the SSPTXD pin and to latch data on the SSPRXD pin. Depending on the frame format selected,

each transmitted bit is driven on either SSPSCLK’s rising or falling edge and sampled on the

opposite clock edge.

This is a read/write register. Ignore reads from reserved bits. Write zeros to reserved bits.

8.7.2 SSP Control Register 1 (SSCR1)

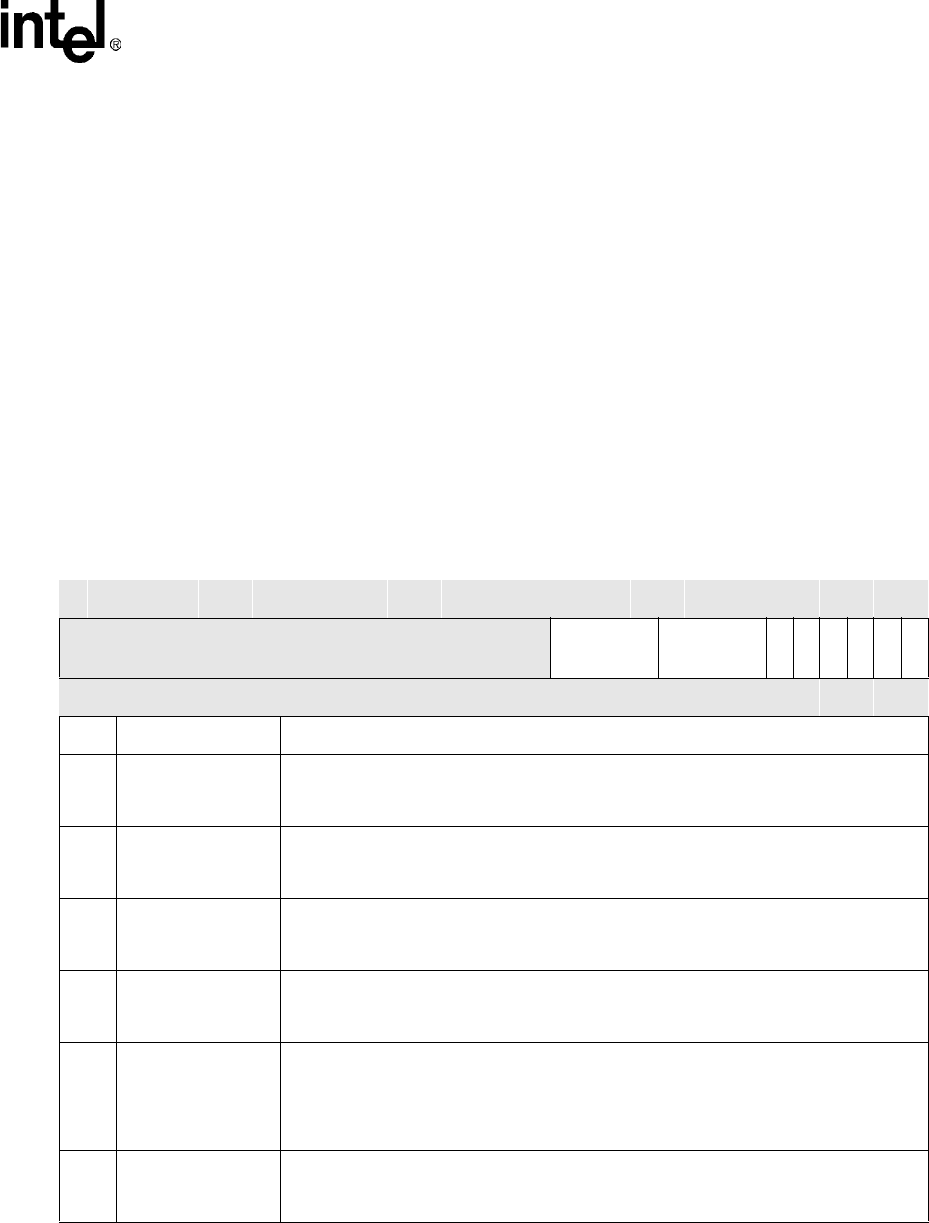

SSCR1, shown in Table 8-3, contains bit fields that control SSP functions.

Table 8-3. SSCR1 Bit Definitions (Sheet 1 of 2)

0x4100_0004 SSP Control Register 1 (SSCR1) Synchronous Serial Port Controller

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

reserved RFT TFT

MWDS

SPH

SPO

LBM

TIE

RIE

Reset X 0x0 0x0 0 0 0 0 0 0

Bits Name Description

0

RIE

Receive FIFO Interrupt Enable

0 = Receive FIFO interrupt is disabled

1 = Receive FIFO interrupt is enabled

1TIE

Transmit FIFO Interrupt Enable

0 = Transmit FIFO interrupt is disabled

1 = 1 - Transmit FIFO interrupt is enabled

2LBM

Loop-Back Mode

0 = Normal serial port operation enabled

1 = Output of transmit serial shifter internally connected to input of receive serial shifter

3 SPO

Motorola SPI SSPSCLK polarity setting:

0 = The inactive or idle state of SSPSCLK is low.

1 = The inactive or idle state of SSPSCLK is high.

4 SPH

Motorola SPI SSPSCLK phase setting:

0 = SSPSCLK is inactive one cycle at the start of a frame and 1/2 cycle at the end of a

frame.

1 = SSPSCLK is inactive 1/2 cycle at the start of a frame and one cycle at the end of a

frame.

5MWDS

Microwire Transmit Data Size:

0 = 8-bit command words are transmitted.

1 = 16-bit command words are transmitted.