Intel® PXA255 Processor Developer’s Manual 7-45

LCD Controller

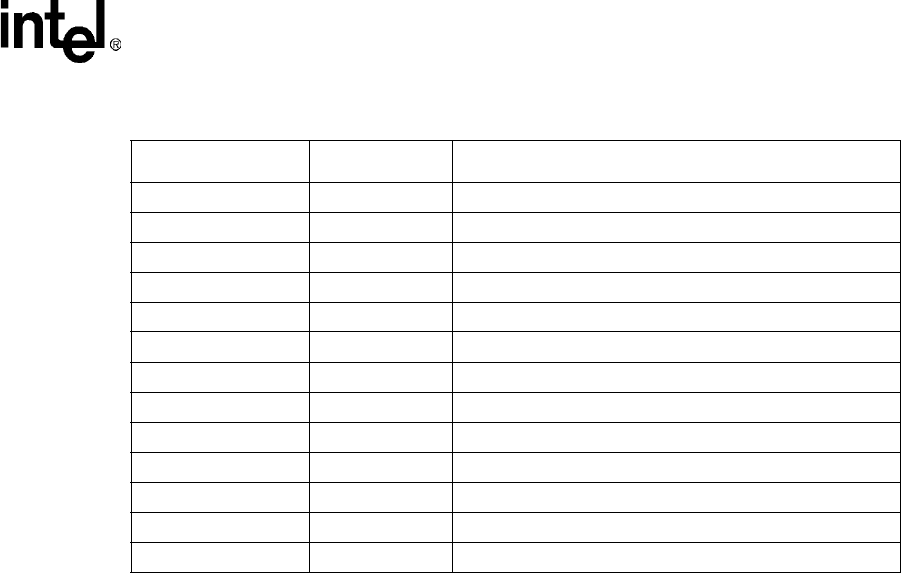

0x4400_0024 FBR1 DMA channel 1 frame branch register

0x4400_0038 LCSR LCD controller status register

0x4400_003C LIIDR LCD controller interrupt ID register

0x4400_0040 TRGBR TMED RGB Seed Register

0x4400_0044 TCR TMED Control Register

0x4400_0200 FDADR0 DMA channel 0 frame descriptor address register

0x4400_0204 FSADR0 DMA channel 0 frame source address register

0x4400_0208 FIDR0 DMA channel 0 frame ID register

0x4400_020C LDCMD0 DMA channel 0 command register

0x4400_0210 FDADR1 DMA channel 1 frame descriptor address register

0x4400_0214 FSADR1 DMA channel 1 frame source address register

0x4400_0218 FIDR1 DMA channel 1 frame ID register

0x4400_021C LDCMD1 DMA channel 1 command register

Table 7-16. LCD Controller Register Summary (Sheet 2 of 2)

Address Name Description