Intel® PXA255 Processor Developer’s Manual 12-39

USB Device Controller

12.6.11 UDC Status/Interrupt Register 0 (USIR0)

USIR0, shown in Table 12-22, and USIR1, shown in Table 12-23, contain bits that are used to

generate the UDC’s interrupt request. Each bit in the UDC status/interrupt registers is logically

ORed together to produce one interrupt request. When the ISR for the UDC is executed, it must

read the UDC status/interrupt register to determine why the interrupt occurred. USIRx is level

sensitive. Be sure to clear USIRx as the last step before exiting the ISR.

The bits in USIR0 and USIR1 are controlled by a mask bit in the UDC Interrupt Control Register

(UICR0/1). The mask bits, when set, prevent a status bit in the USIRx from being set. If the mask

bit for a particular status bit is cleared and an interruptible condition occurs, the status bit is set. To

clear status bits, the core must write a 1 to the position to be cleared. The interrupt request for the

UDC remains active as long as the value of the USIRx is non-zero.

12.6.11.1 Endpoint 0 Interrupt Request (IR0)

The endpoint 0 interrupt request is set if the IM0 bit in the UDC control register is cleared and, in

the UDC endpoint 0 control/status register, the OUT packet ready bit is set, the IN packet ready bit

is cleared, or the sent STALL bit is set. The IR0 bit is cleared by writing a 1 to it.

12.6.11.2 Endpoint 1 Interrupt Request (IR1)

The interrupt request bit is set if the IM1 bit in the UDC interrupt control register is cleared and the

IN packet complete (TPC) in UDC endpoint 1 control/status register is set. The IR1 bit is cleared

by writing a 1 to it.

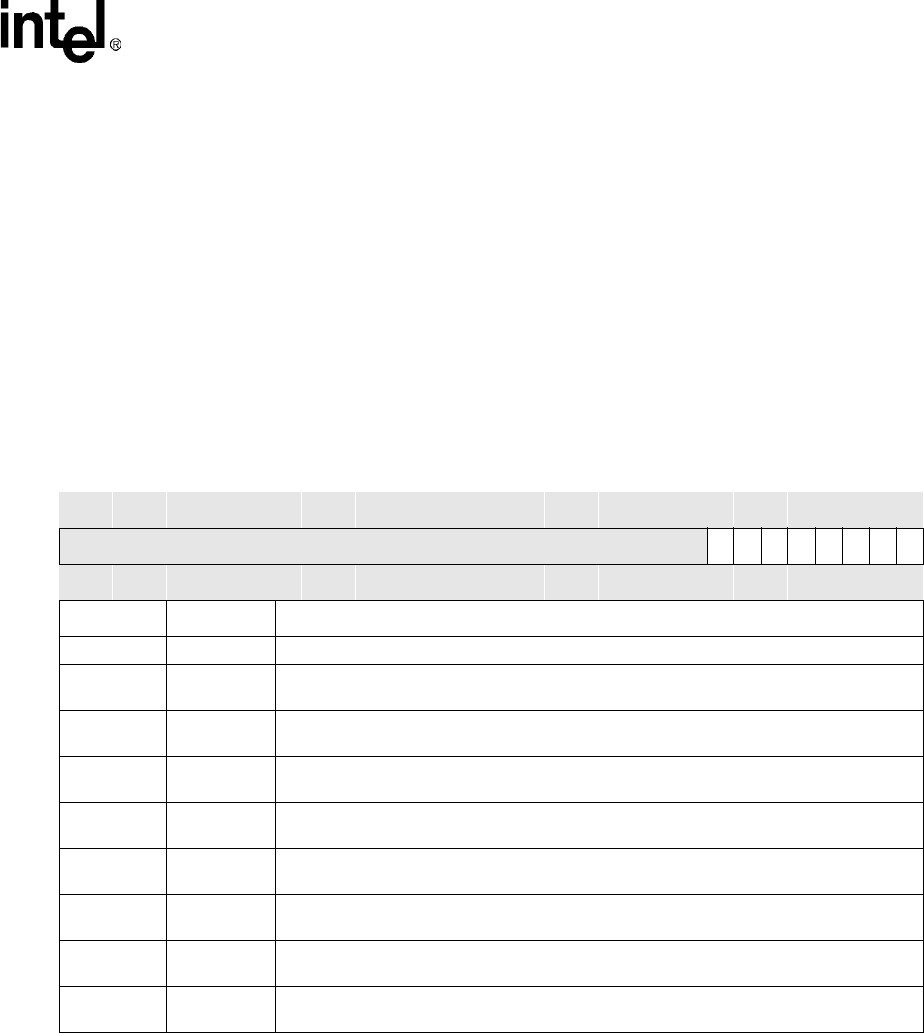

Table 12-22. USIR0 Bit Definitions

0x 4060_0058 USIR0 USB Device Controller

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

reserved

IR7

IR6

IR5

IR4

IR3

IR2

IR1

IR1

Reset x x x x x x x x x x x x x x x x x x x x x x x x 0 0 0 0 0 0 0 0

Bits Name Description

31:8 — reserved

7IR7

Interrupt Request Endpoint 7 (read/write 1 to clear)

1 = Endpoint 7 needs service.

6IR6

Interrupt Request Endpoint 6 (read/write 1 to clear)

1 = Endpoint 6 needs service.

5IR5

Interrupt Request Endpoint 5 (read/write 1 to clear)

1 = Endpoint 5 needs service.

4IR4

Interrupt Request Endpoint 4 (read/write 1 to clear)

1 = Endpoint 4 needs service.

3IR3

Interrupt Request Endpoint 3 (read/write 1 to clear)

1 = Endpoint 3 needs service.

2IR2

Interrupt Request Endpoint 2 (read/write 1 to clear)

1 = Endpoint 2 needs service.

1IR1

Interrupt Request Endpoint 1 (read/write 1 to clear)

1 = Endpoint 1 needs service.

0IR0

Interrupt Request Endpoint 0 (read/write 1 to clear)

1 = Endpoint 0 needs service.