3-34 Intel® PXA255 Processor Developer’s Manual

Clocks and Power Manager

3.6 Clocks Manager Registers

The Clocks Manager contains three registers:

• Core Clock Configuration Register (CCCR)

• Clock Enable Register (CKEN)

• Oscillator Configuration Register (OSCC)

3.6.1 Core Clock Configuration Register (CCCR)

The CCCR, shown in Table 3-20, controls the core clock frequency, from which the core, memory

controller, LCD controller, and DMA controller frequencies are derived. The crystal frequency to

memory frequency multiplier (L), memory frequency to run mode frequency multiplier (M), and

run mode frequency to turbo mode frequency multiplier (N) are set in this register. The clock

frequencies are shown below.

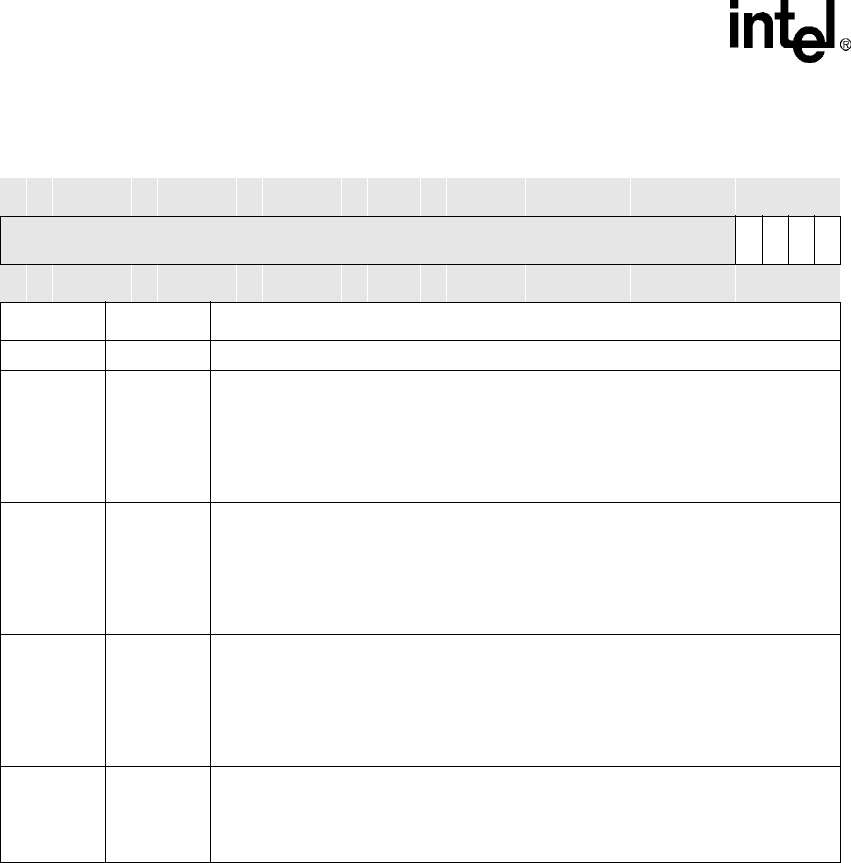

Table 3-19. RCSR Bit Definitions

0x40F0_0030 RCSR Clocks and Power Manager

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

reserved

GPR

SMR

WDR

HWR

Reset 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1

Bits Name Description

[31:4] — reserved

3GPR

GPIO Reset.

0 – GPIO reset has not occurred since the last time the CPU or hardware reset cleared

this bit.

1 – GPIO reset has occurred since the last time the CPU or hardware reset cleared this

bit.

Cleared by hardware reset and by setting to a 1.

2SMR

Sleep Mode.

0 – Sleep mode has not occurred since the last time the CPU or hardware reset cleared

this bit.

1 – Sleep mode has occurred since the last time the CPU or hardware reset cleared

this bit.

Cleared by hardware reset and by setting to a 1.

1WDR

Watchdog Reset.

0 – Watchdog reset has not occurred since the last time the CPU or hardware reset

cleared this bit.

1 – Watchdog reset has occurred since the last time the CPU or hardware reset cleared

this bit.

Cleared by hardware reset and by setting to a 1.

0HWR

Hardware Reset.

0 – Hardware reset has not occurred since the last time the CPU cleared this bit.

1 – Hardware reset has occurred since the last time the CPU cleared this bit.

Set by hardware reset. Cleared by setting to a 1.