15-30 Intel® PXA255 Processor Developer’s Manual

MultiMediaCard Controller

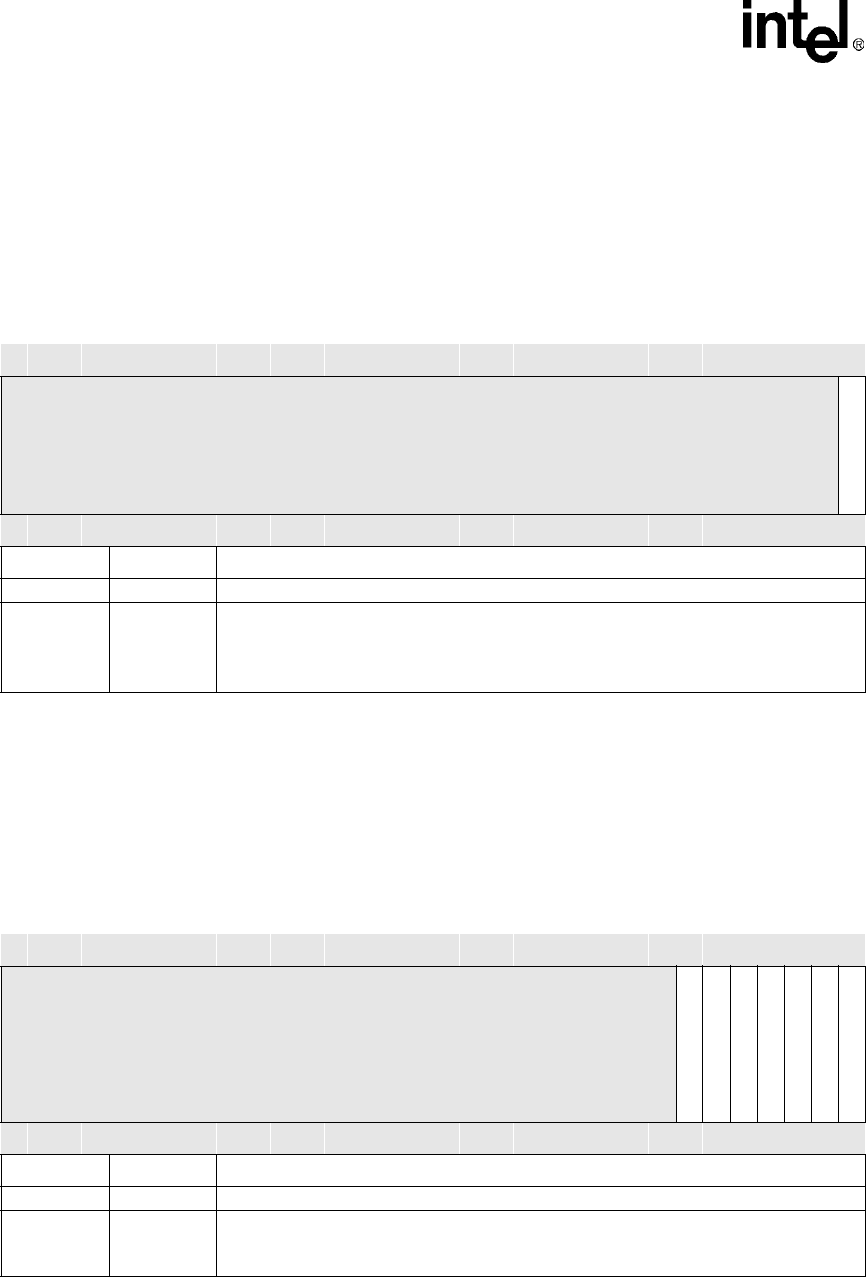

15.5.10 MMC_PRTBUF Register (MMC_PRTBUF)

MMC_PRTBUF, shown in Table 15-14, is used when MMC_TXFIFO is partially written. The

FIFOs swap when either FIFO is full (32 bytes) or the MMC_PRTBUF register is set to a 1.

This is a read/write register. Ignore reads from reserved bits. Write zeros to reserved bits.

15.5.11 MMC_I_MASK Register (MMC_I_MASK)

MMC_I_MASK, shown in Table 15-15, masks off the various interrupts when set to a 1.

This is a read/write register. Ignore reads from reserved bits. Write zeros to reserved bits.

Table 15-14. MMC_PRTBUF Bit Definitions

Physical Address

0x4110_0024

MMC_PRTBUF Register MultiMediaCard Controller

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

reserved

BUF_PART_FULL

Reset 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Bits Name Description

31:1 — reserved

0

BUF_PART_F

ULL

Buffer Partially Full

0 – Buffer is not partially full.

1 – Buffer is partially full and must be swapped to the other transmit buffer

Software must clear this bit before sending the next command.

Table 15-15. MMC_I_MASK Bit Definitions (Sheet 1 of 2)

Physical Address

0x4110_0028

MMC_I_MASK Register MultiMediaCard Controller

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

reserved

TXFIFO_WR_REQ

RXFIFO_RD_REQ

CLK_IS_OFF

STOP_CMD

END_CMD_RES

PRG_DONE

DATA_TRAN_DONE

Reset 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1

Bits Name Description

31:7 — reserved

6

TXFIFO_WR_

REQ

Transmit FIFO Write Request

0 – Not masked

1 – Masked