Intel® PXA255 Processor Developer’s Manual 6-79

Memory Controller

11. Optionally, in systems that contain SDRAM or Synchronous Static memory, enable auto-

power-down by setting MDREFR[APD].

6.12 GPIO Reset Procedure

On a GPIO Reset, the Memory Controller registers keep the values they had before the reset. No

new configuration programming is required. However, SDRAM refreshes do not occur during the

reset time. After nRESET_OUT is deasserted, the memory controller will continue refreshing. By

ensuring a refresh time for SDRAM that is smaller than the default, it is possible to preserve the

SDRAM contents. To do this, follow this procedure:

The SDRAM refresh time is chosen by taking the specified refresh time, typically 64 ms, and

subtracting the GPIO Reset time (found in the Intel® PXA255 Applications Processors Electrical,

Mechanical, and Thermal Specification). For example, the GPIO Reset time is ~360 microseconds,

leaving an SDRAM refresh time of (64 ms - .360 ms) = 63.64 ms. Use this time to program the

MDREFR[DRI].

In the boot code, determine the type of reset. If the reset was a GPIO reset, then refresh all the

SDRAM rows. Refreshing all the SDRAM rows preserves their value in case GPIO reset occurs

again.

After all the SDRAM rows have been refreshed, enable GPIO reset

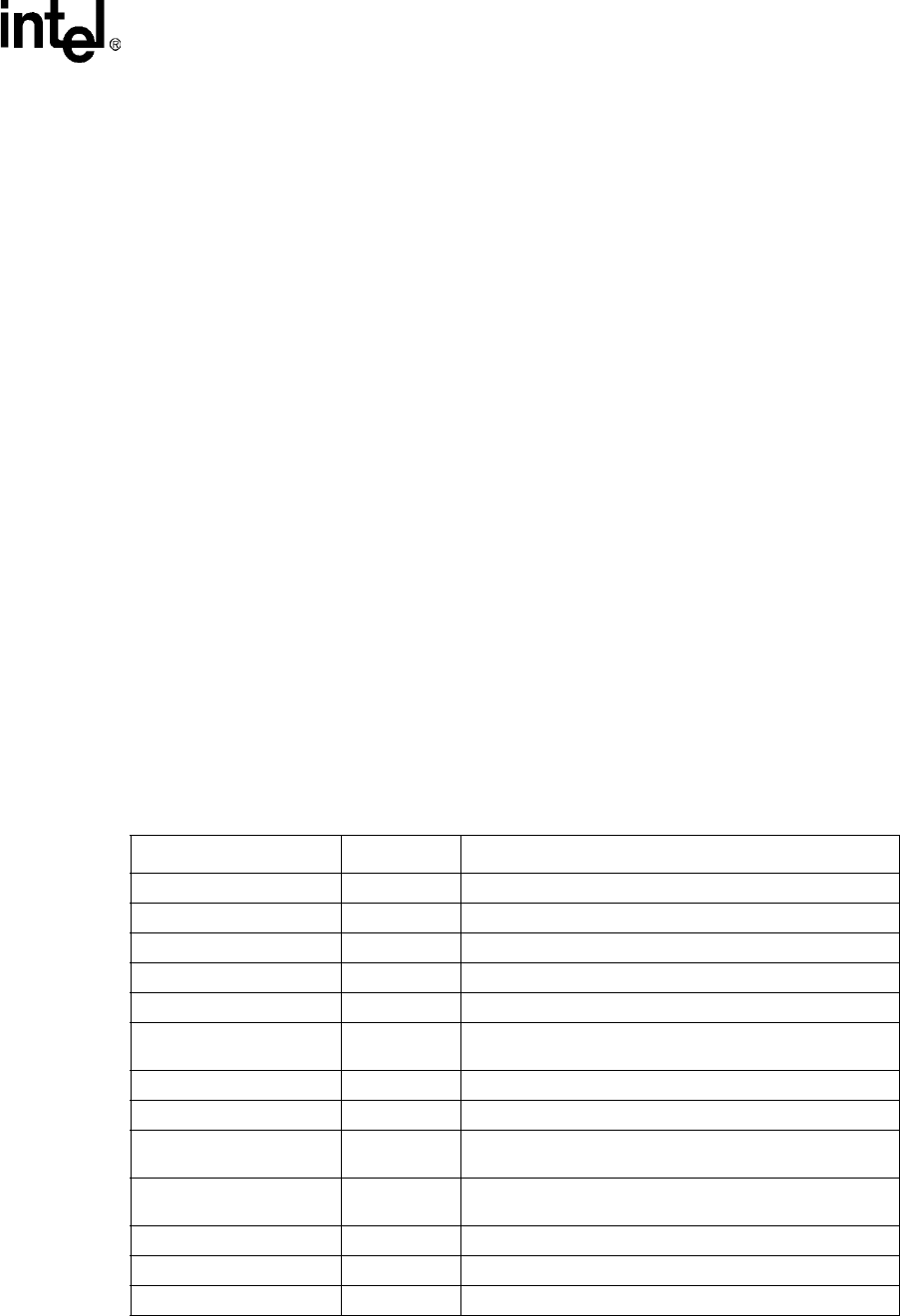

6.13 Memory Controller Register Summary

Table 6-40 shows the registers associated with the memory interface and the physical addresses

used to access them. These registers must be mapped as non-cacheable and non-bufferable and can

only be a single word access. They are grouped together in one page and all have the same memory

protections.

Table 6-40. Memory Controller Register Summary (Sheet 1 of 2)

Physical Address Symbol Register Name

0x4800_0000 MDCNFG SDRAM Configuration Register

0x4800_0004 MDREFR SDRAM Refresh Control Register

0x4800_0008 MSC0 Static Memory Control Register 0

0x4800_000C MSC1 Static Memory Control Register 1

0x4800_0010 MSC2 Static Memory Control Register 2

0x4800_0014 MECR

Expansion Memory (16-bit PC Card / Compact Flash) Bus

Configuration register

0x4800_001C SXCNFG Synchronous Static Memory Control Register

0x4800_0024 SXMRS MRS value to be written to SMROM

0x4800_0028 MCMEM0

Card interface Common Memory Space Socket 0 Timing

Configuration

0x4800_002C MCMEM1

Card interface Common Memory Space Socket 1 Timing

Configuration

0x4800_0030 MCATT0 Card interface Attribute Space Socket 0 Timing Configuration

0x4800_0034 MCATT1 Card interface Attribute Space Socket 1 Timing Configuration

0x4800_0038 MCIO0 Card interface I/O Space Socket 0 Timing Configuration