5-24 Intel® PXA255 Processor Developer’s Manual

DMA Controller

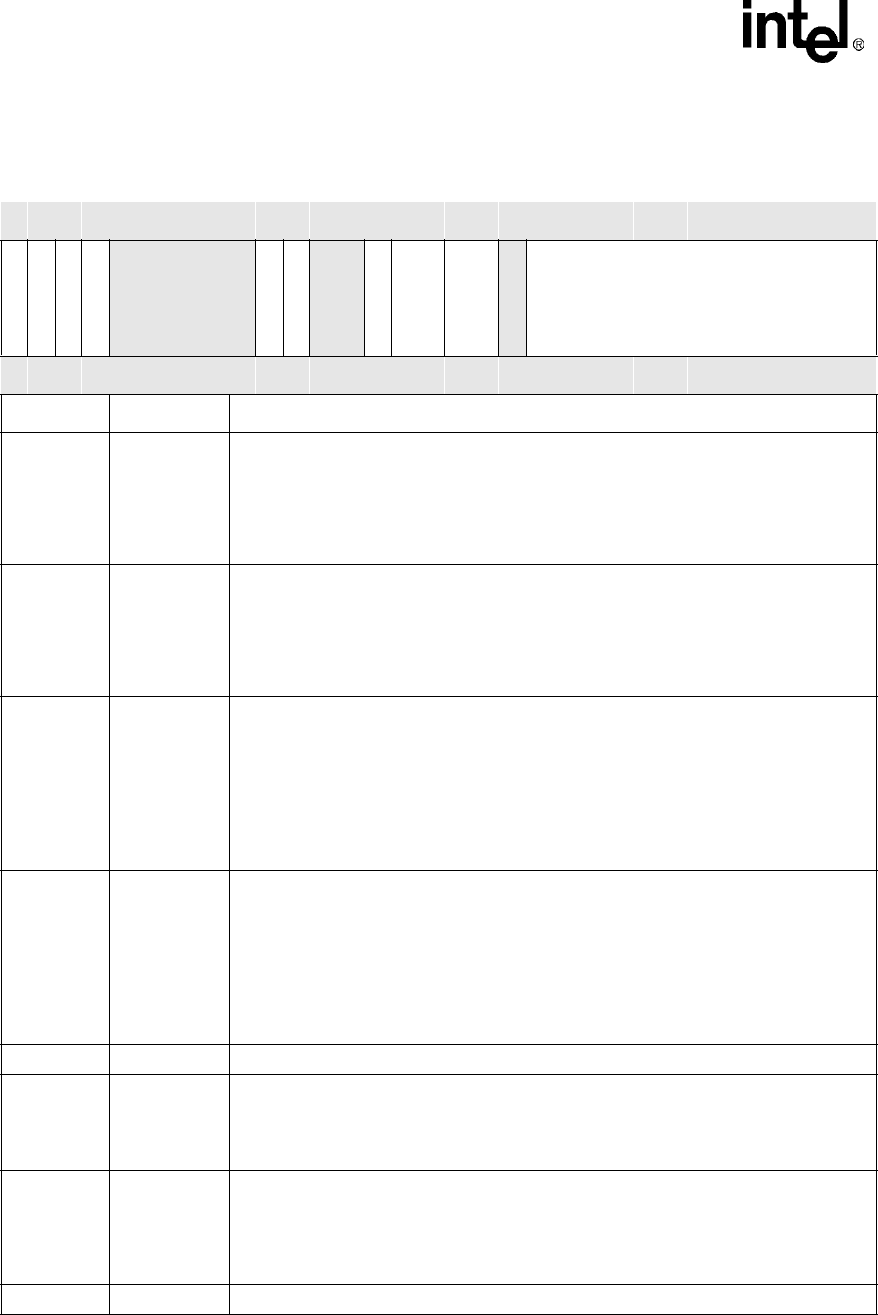

Table 5-12. DCMDx Bit Definitions (Sheet 1 of 2)

0x4000_02xC DMA Command Register (DCMDx) DMA Controller

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

INCSRCADDR

INCTRGADDR

FLOWSRC

FLOWTRG

reserved

STARTIRQEN

ENDIRQEN

reserved

ENDIAN

SIZE

WIDTH

reserved

LENGTH

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Bits Name Description

31 INCSRCADDR

Source Address Increment Setting. (read / write).

0 – Do not increment Source Address

1 – Increment Source Address at the end of each internal bus transaction initiation by

DCMD[SIZE]

If the source address is an internal peripheral’s FIFO address or external IO address, the

address is not incremented on each successive access. In this case, this bit must be 0.

30 INCTRGADDR

Target Address Increment Setting. (read / write).

0 – Do not increment Target Address

1 – Increment Target Address at the end of each internal bus transaction initiated by

DCMD[SIZE]

If the target address is an internal peripheral’s FIFO address or external IO address, the

address is incremented on each successive access. In this cases the bit must be 0.

29 FLOWSRC

Flow Control by the source. (read / write).

0 – Start the data transfer immediately.

1 – Wait for a request signal before initiating the data transfer.

Indicates the flow control of the source. This bit must be ‘1’ if the source is an onchip or

external peripheral.

If either the DCMD[FLOWSRC] or DCMD[FLOWTRG] bit is set, the current DMA does not

initiate a transfer until it receives a request. Do not set both the DCMD[FLOWTRG] and

DCMD[FLOWSRC] bit to1.

28 FLOWTRG

Flow Control by the target. (read / write).

0 – Start the data transfer immediately.

1 – Wait for a request signal before initiating the data transfer.

Indicates the Flow Control of the target. This bit must be ‘1’ if the target is an onchip or

external peripheral.

If either the DCMD[FLOWSRC] or DCMD[FLOWTRG] bit is set, the current DMA does not

initiate a transfer until it receives a request. Do not set both the DCMD[FLOWTRG] and

DCMD[FLOWSRC] bit to 1.

27:23 — reserved

22 STARTIRQEN

Start Interrupt Enable (read / write), Reserved for the No-Descriptor Fetch Mode

0 – no interrupt is generated.

1 – Allow interrupt to pass when the descriptor (i.e., 4 words) for the channel are loaded.

Sets DCSR[StartIntr] interrupt for the channel when this descriptor is loaded.

21 ENDIRQEN

End Interrupt Enable (read / write).

0 – no interrupt is generated.

1 – set DCSR[EndIntr] interrupt for the channel when DCMD[LENGTH] is decreased to

zero.

Indicates that the interrupt is enabled as soon as the data transfer is completed.

20:19 — reserved