17-20 Intel® PXA255 Processor Developer’s Manual

Hardware UART

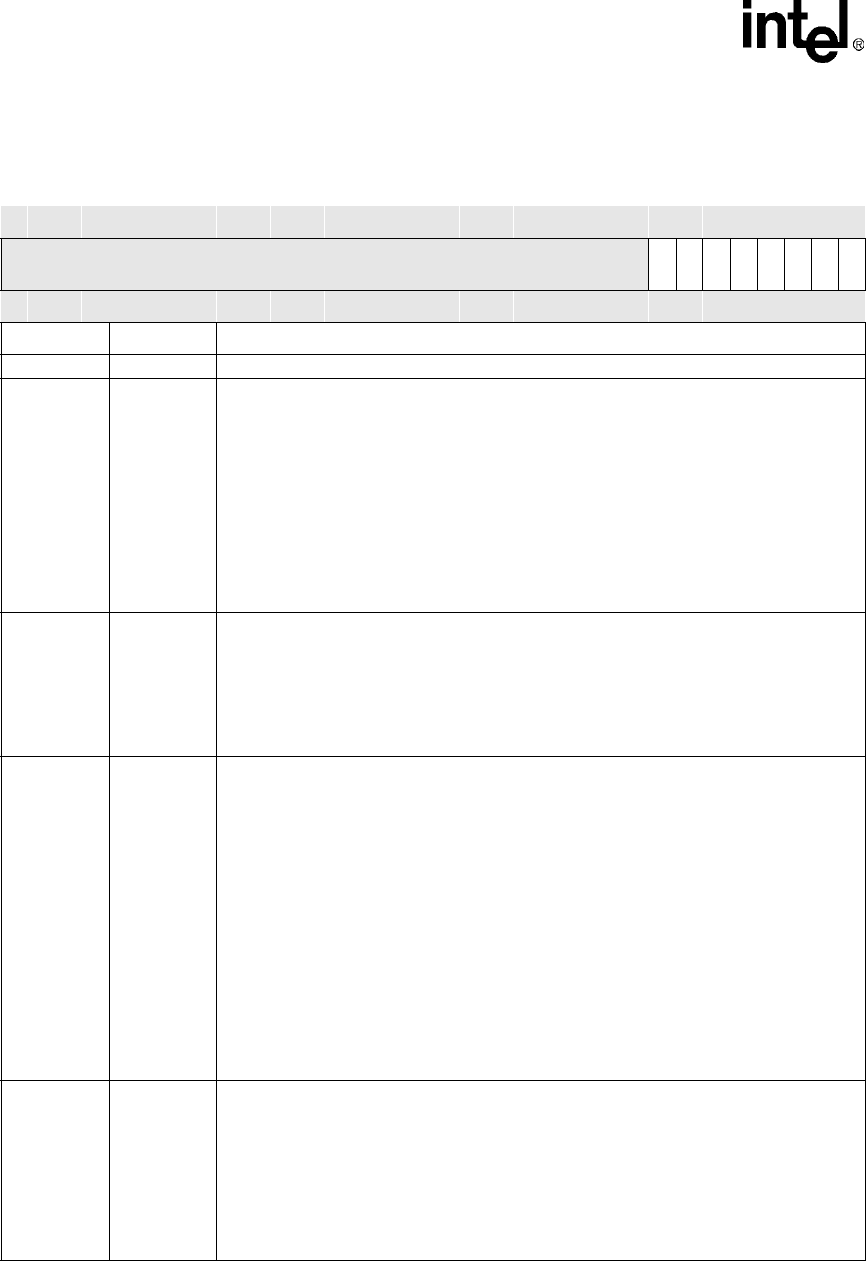

Table 17-15. LSR Bit Definitions (Sheet 1 of 2)

Physical Address

0x4160_0014

Line Status Register (LSR) PXA255 Processor Hardware UART

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

reserved

FIFOE

TEMT

TDRQ

BI

FE

PE

OE

DR

Reset ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? 0 1 1 0 0 0 0 0

Bits Name Description

31:8 — reserved

7FIFOE

FIFO ERROR STATUS

In non-FIFO mode, this bit is 0. In FIFO mode, FIFOE is set to 1 when there is at least one

parity error, framing error, or break indication for any of the characters in the FIFO. A

processor read to the LSR does not reset this bit. FIFOE is reset when all erroneous

characters have been read from the FIFO. If DMA requests are enabled (IER bit 7 is set to

1) and FIFOE is set to 1, the error interrupt is generated and no receive DMA request is

generated even when the receive FIFO reaches the trigger threshold. Once the errors have

been cleared, by reading the FIFO, DMA requests are automatically re-enabled. If DMA

requests are not enabled (IER bit 7 is set to 0), then FIFOE set to 1 does not generate an

error interrupt.

0 = No FIFO or no errors in receiver FIFO

1 = At least one character in receiver FIFO has errors

6TEMT

TRANSMITTER EMPTY

Set when the Transmit Holding register and the Transmitter Shift register are both empty. It

is cleared when either the Transmit Holding register or the Transmitter Shift register

contains a data character. In FIFO mode, TEMT is set when the transmitter FIFO and the

Transmit Shift register are both empty.

0 = There is data in the Transmit Shift register, the Transmit Holding register, or the FIFO

1 = All the data in the transmitter has been shifted out

5TDRQ

TRANSMIT DATA REQUEST

Indicates that the UART is ready to accept a new character for transmission. In addition,

this bit causes the UART to issue an interrupt to the processor when the transmit data

request interrupt enable is set high and generates the DMA request to the DMA controller if

DMA requests and FIFO mode are enabled.

In non-FIFO mode, TDRQ is set when a character is transferred from the Transmit Holding

register into the Transmit Shift register. The bit is cleared with the loading of the Transmit

Holding register.

In FIFO mode, TDRQ is set to 1 when half of the characters in the FIFO have been loaded

into the Shift register if FCR[TIL]=0, or the FIFO is empty and FCR[TIL]=1, or the RESETTF

bit in FCR has been set. It is cleared when the FIFO has more data than required by

FCR[TIL].

If more than 64 characters are loaded into the FIFO, the excess characters are lost.

0 = There is data in Transmit Holding register or FIFO waiting to be shifted out

1 = Transmit FIFO has half or less than half data (FCR[TIL]=0), or the transmit FIFO is

empty (FCR[TIL]=1), or the UART is waiting for data (non-FIFO mode)

4BI

BREAK INTERRUPT

BI is set when the received data input is held low for longer than a full word transmission

time (that is, the total time of start bit + data bits + parity bit + stop bits). The break indicator

is reset when the processor reads the LSR. In FIFO mode, only one character equal to

0x00, is loaded into the FIFO regardless of the length of the break condition. BI shows the

break condition for the character at the front of the FIFO, not the most recently received

character.

0 = No break signal has been received

1 = Break signal received