Intel® PXA255 Processor Developer’s Manual 5-1

DMA Controller 5

This chapter describes the on-chip DMA controller (DMAC) for the PXA255 processor. The

DMAC transfers data to and from main memory in response to requests generated by internal and

external peripherals. The peripherals do not directly supply addresses and commands to the

memory system. The DMAC has 16 DMA channels, 0 through 15, and every DMA request from

the peripheral generates at least one memory bus cycle.

5.1 DMA Description

The DMAC supports only flow-through transfers.

Flow-through data passes through the DMAC before the data is latched by the destination in its

buffers/memory. This DMAC can perform memory-to-memory moves with flow-through transfers.

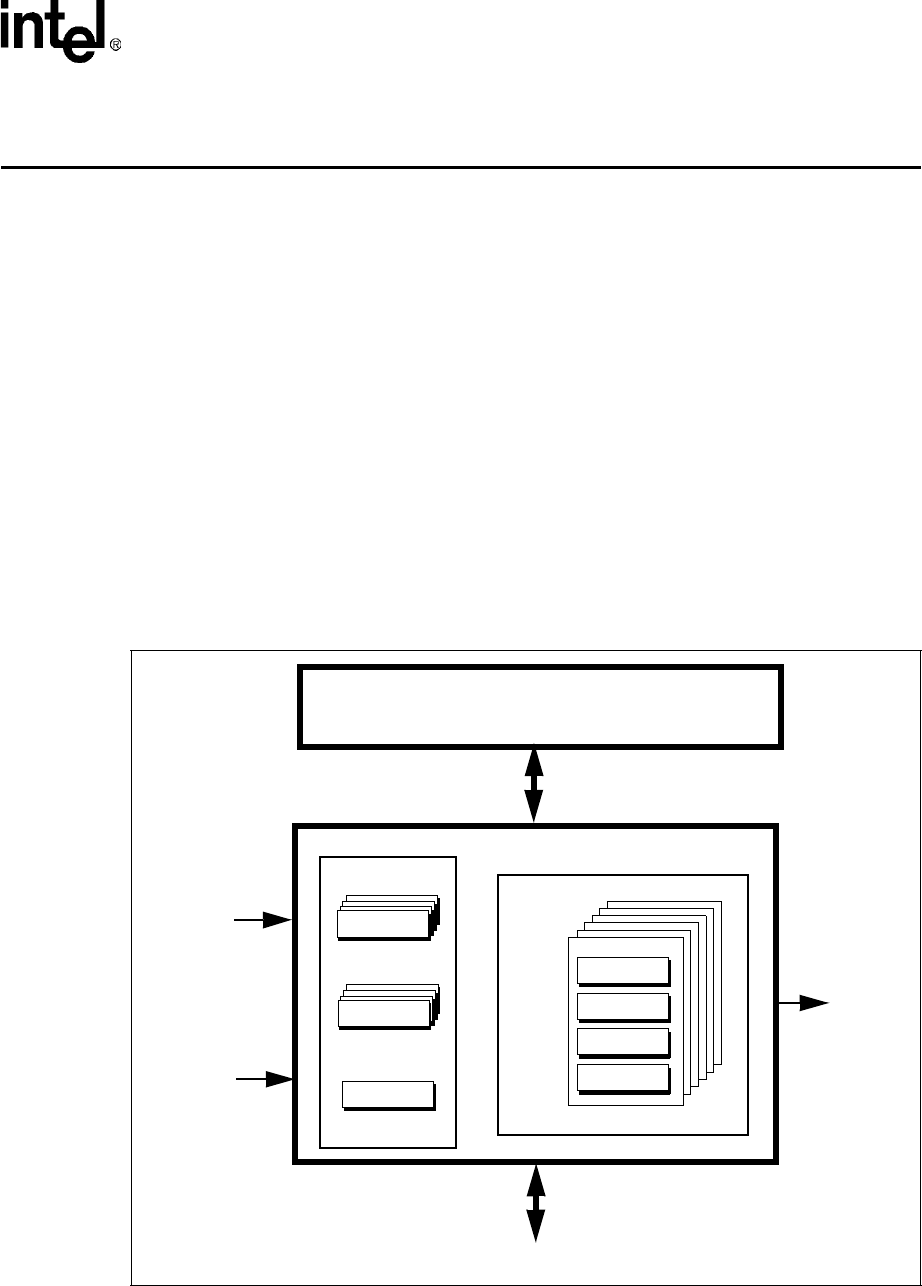

Figure 5-1 provides an overview of the DMAC. Table 5-1 provides a list of the DMAC signals and

descriptions.

Figure 5-1. DMAC Block Diagram

DDADR0

DSADR0

DTADR0

DCMD0

Channel 0

Channel 15

16 DMA Channels

DRCMR0

Control Registers

System Bus (internal)

Peripheral Bus

DREQ[1:0]

PREQ[37:0]

DMA_IRQ

DMA Controller

DINT

DCSR0

(external)

(internal)

(internal)

(internal)

Memory Controller