16-26 Intel® PXA255 Processor Developer’s Manual

Network SSP Serial Port

Bits that cause an interrupt signal the request as long as the bit is set. The interrupt clears when the

bits clear. Read and write bits are called status bits (status bits are referred to as sticky and once set

by hardware, they must be cleared by software); Read-only bits are called flags. Writing a 1 to a

status bit clears it; writing a 0 has no effect. Read-only flags are set and cleared by hardware; writes

have no effect. The reset state of read-write bits is zero and all bits return to their reset state when

SSCR0[SSE] is cleared. Additionally, some bits that cause interrupts have corresponding mask bits

in the control registers and are indicated in the section headings that follow.

Set the desired values for this register before enabling the SSP (via SSCR0[SSE]).

These are read/write registers. Ignore reads from reserved bits. Write zeros to reserved bits.

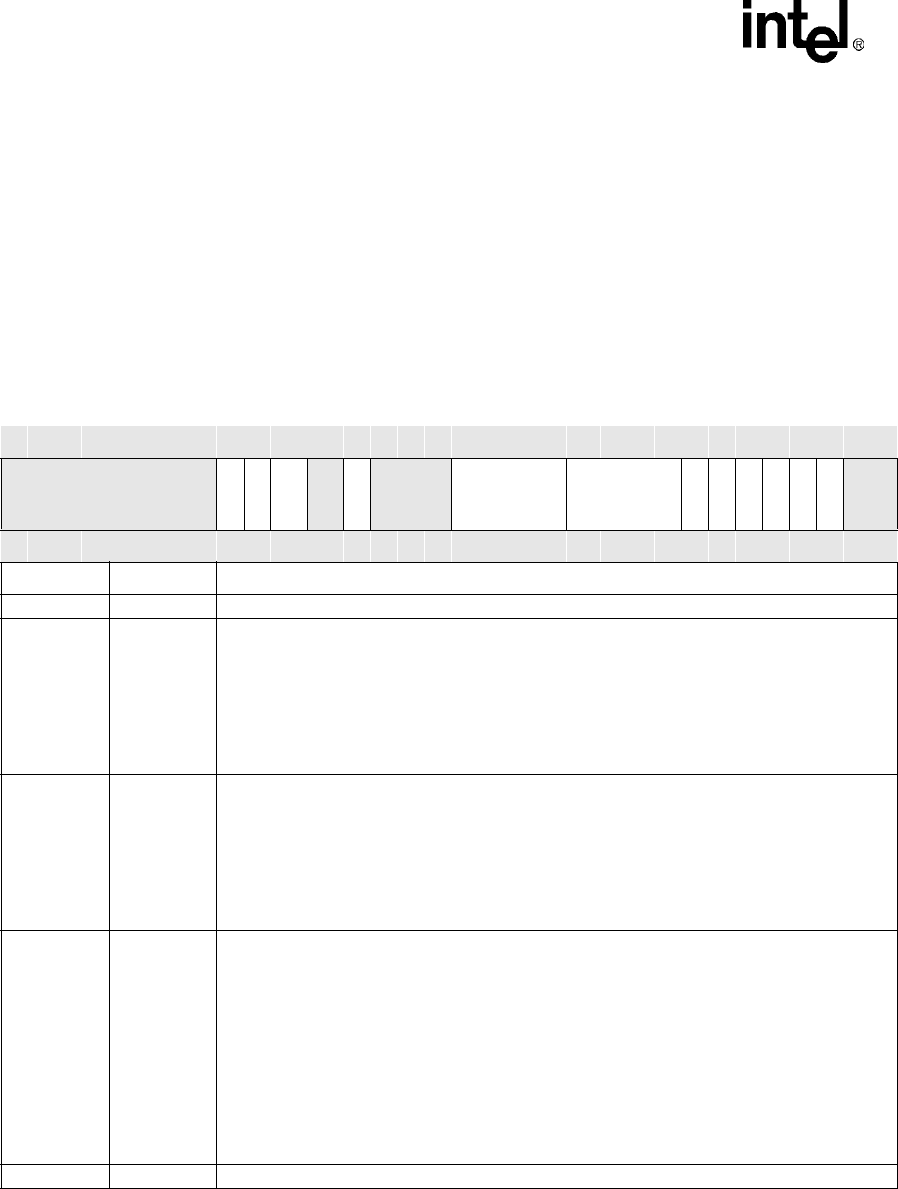

Table 16-8. SSSR Bit Definitions (Sheet 1 of 3)

0x4140_0008 SSSR Network SSP Serial Port

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

reserved

BCE

CSS

TUR

reserved

TINT

reserved

RFL

TFL

ROR

RFS

TFS

BSY

RNE

TNF

reserved

Reset ? ? ? ? ? ? ? ? 0 0 0 ? 0 ? ? ? 1 1 1 1 0 0 0 0 0 0 0 0 0 1 ? ?

Bits Name Description

31:24 — reserved

23 BCE

BIT COUNT ERROR:

Indicates that the SSP has detected the SSPSFRM signal asserted at an incorrect time. This bit

will cause an interrupt if SSCR1[BCE] is set. The SSP will ignore the current sample and the

next sample in order to re-synchronize with the master.

Write one to clear this bit.

0 – SSPSFRM has not been asserted out of synchronization.

1 – SSPSFRM has been asserted out of synchronization.

22 CSS

CLOCK SYNCHRONIZATION STATUS:

A read-only bit that indicates the SSP is busy synchronizing the control signals. This bit is only

valid when the SSP is a slave to frame.

Software must wait until this bit is a 0 before allowing an external device to assert the SSPSFRM

signal.

0 – The SSP is ready for slave operations.

1 – The SSP is busy synchronizing slave mode signals.

21 TUR

TRANSMIT FIFO UNDER RUN:

Indicates that the transmitter tried to send data from the transmit FIFO when the transmit FIFO

was empty. When set, an interrupt is generated to the CPU that cannot be locally masked by any

SSP register bit. Setting TUR does not generate any DMA service request. To clear TUR,

software sets it. TUR remains set until cleared by software writing a one to it which also reset its

Interrupt request. Writing a zero to this bit does not affect TUR.

TUR can be set only when the port is a slave to the FRAME signal (SSCR1[SFRMDIR] set) and

is not set if the port is in receive-without-transmit mode (SSCR1[RWOT] set).

Write one to clear this bit.

0 – Transmit FIFO has not experienced an under run

1 – Attempted read from the transmit FIFO when the FIFO was empty, request interrupt.

20 — reserved