Intel® PXA255 Processor Developer’s Manual 8-1

Synchronous Serial Port Controller 8

This chapter describes the Synchronous Serial Port Controller’s (SSPC) signal definitions and

operation for the PXA255 processor usage.

8.1 Overview

The SSPC is a full-duplex synchronous serial interface and can connect to a variety of external

analog-to-digital (A/D) converters, audio and telecom codecs, and other devices that use serial

protocols for transferring data. The SSPC supports National’s Microwire* , Texas Instruments’

Synchronous Serial Protocol* (SSP), and Motorola’s Serial Peripheral Interface* (SPI) protocol.

The SSPC operates in master mode (the attached peripheral functions as a slave) and supports

serial bit rates from 7.2 KHz to 1.84 MHz. Serial data formats may range from 4 to 16 bits in

length. The SSPC provides 16 entries deep x 16 bits wide transmit and receive data FIFOs.

The FIFOs may be loaded or emptied by the Central Processor Unit (CPU) using programmed I/O,

or DMA burst transfers of 4 or 8 half-words per transfer while receiving or transmitting.

8.2 Signal Description

This section describes the SSPC signals.

8.2.1 External Interface to Synchronous Serial Peripherals

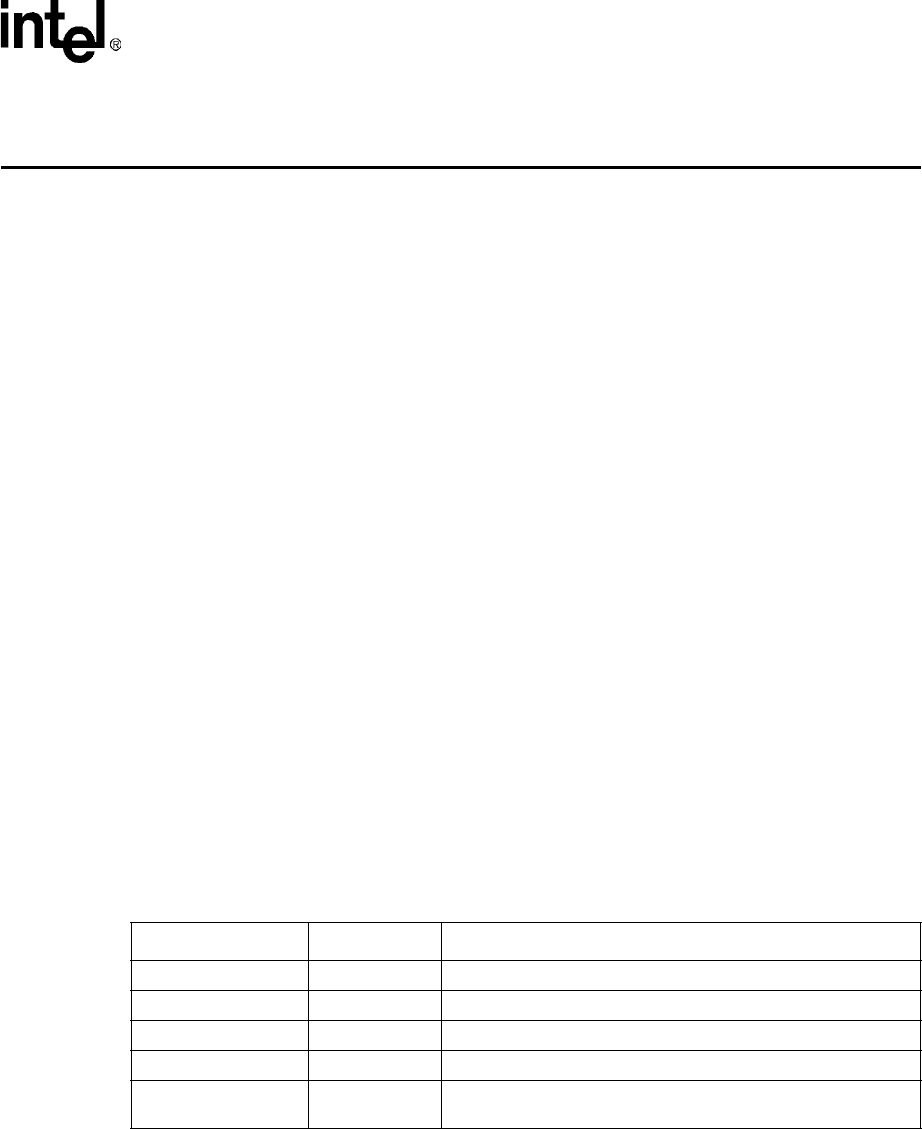

Table 8-1 lists the external signals that connect the SSP to an external peripheral.

SSPSCLK is the bit-rate clock driven from the SSPC to the peripheral. SSPSCLK is toggled only

when data is actively being transmitted and received.

SSPSFRM is the framing signal, indicating the beginning and the end of a serialized data word.

SSPTXD and SSPRXD are the Transmit and Receive serial data lines.

Table 8-1. External Interface to Codec

Name Direction Description

SSPSCLK Output Serial bit-rate clock

SSPSFRM Output Frame indicator

SSPTXD Output Transmit Data (serial data out)

SSPRXD Input Receive Data (serial data in)

SSPEXTCLK Input

External clock which can be selected to drive the serial clock

(SSPSCLK)