5-18 Intel® PXA255 Processor Developer’s Manual

DMA Controller

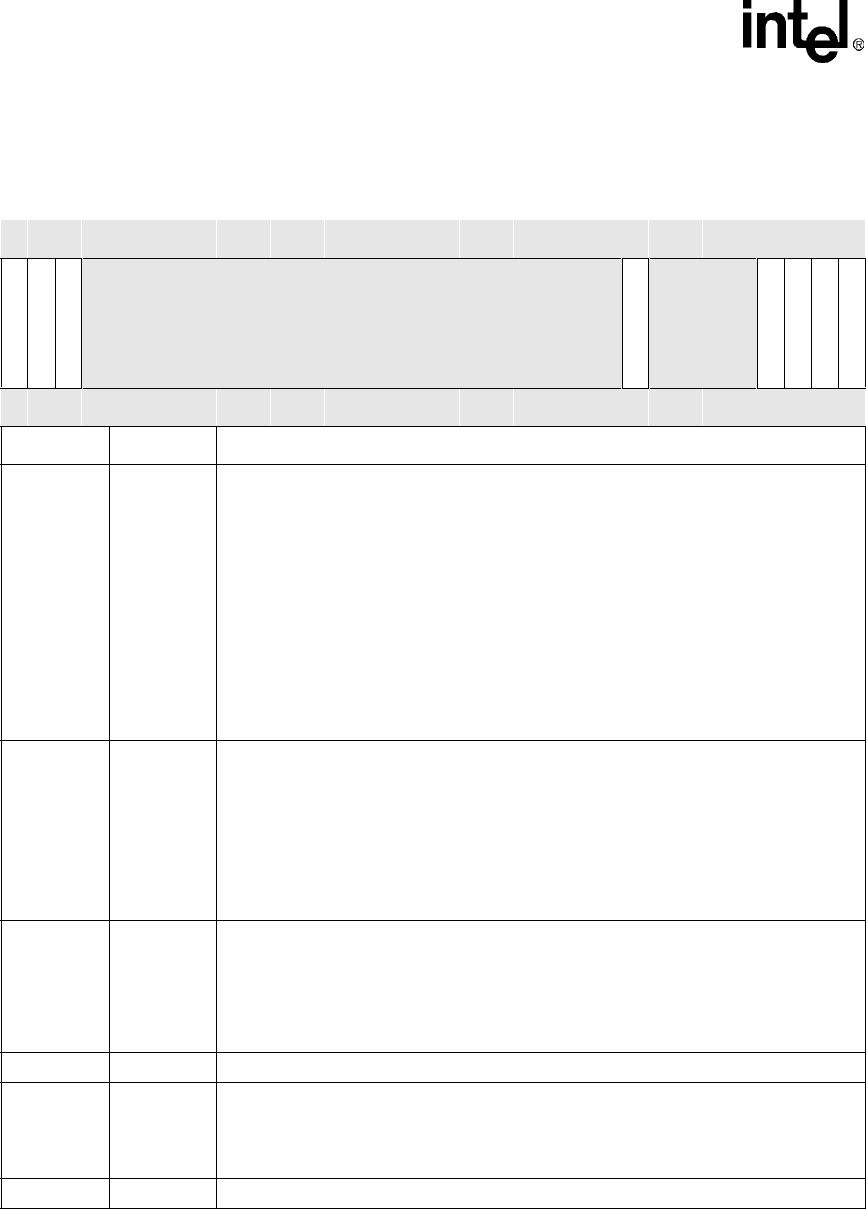

Table 5-7. DCSRx Bit Definitions (Sheet 1 of 2)

Physical Address

0x4000_0000 - 0x4000_003C

DMA Channel Control/Status

Register (DCSRx)

DMA Controller

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

RUN

NODESCFETCH

STOPIRQEN

reserved

REQPEND

reserved

STOPSTATE

ENDINTR

STARTINTR

BUSERRINTR

Reset 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0

Bits Name Description

31 RUN

Run Bit (read / write).

0 – stops the channel

1 – starts the channel

Lets software start or stop the channel. If the run bit is cleared in the middle of the burst, the

burst will complete before the channel is stopped.

Software must write to DDADRx before it sets this bit for Descriptor Fetch Mode.

After the channel stops, the DCSR[STOPSTATE] bit is set to 1. Software must poll the

DCSR[STOPSTATE] bit to determine the channel’s status or set the STOPIRQEN to force

an interrupt after the channel stops. Software must write a 1 to the bit to restart a stopped

channel.

After clearing the run bit to stop the channel, an end interrupt is not guaranteed to happen if

the length bits, DCMDx[LENGTH], is zero. Software must determine if the transfer is done

after clearing the run bit.

30

NODESC

FETCH

No-Descriptor Fetch (read / write).

0 – Descriptor Fetch Mode

1 – No-Descriptor Fetch Mode

Determines if the channel has a descriptor.

If this bit is set to a 0, the channel is in Descriptor Fetch Mode. See Section 5.1.4.2 for

information on the DMAC registers.

If this bit is set to a 1, the channel is in No-Descriptor Fetch Mode. See Section 5.1.4.1 for

information on the DMAC registers.

29 STOPIRQEN

Stop Interrupt Enable (read / write).

0 – no interrupt if the channel is in uninitialized or stopped state

1 – enables an interrupt if the channel is in uninitialized or stopped state

Allows an interrupt to pass to the interrupt controller if the DCSR[STOPSTATE] bit is 1. If

the DCSR[STOPINTEN] bit is 0, the interrupt is not generated after the channel stops. If

software writes a 1 to this bit before the channel starts, an interrupt is generated.

28:9 — reserved

8 REQPEND

Request Pending (read-only).

0 – no pending request

1 – the channel has a pending request

Indicates that the DMA channel has a pending request.

7:4 — reserved