Intel® PXA255 Processor Developer’s Manual 6-41

Memory Controller

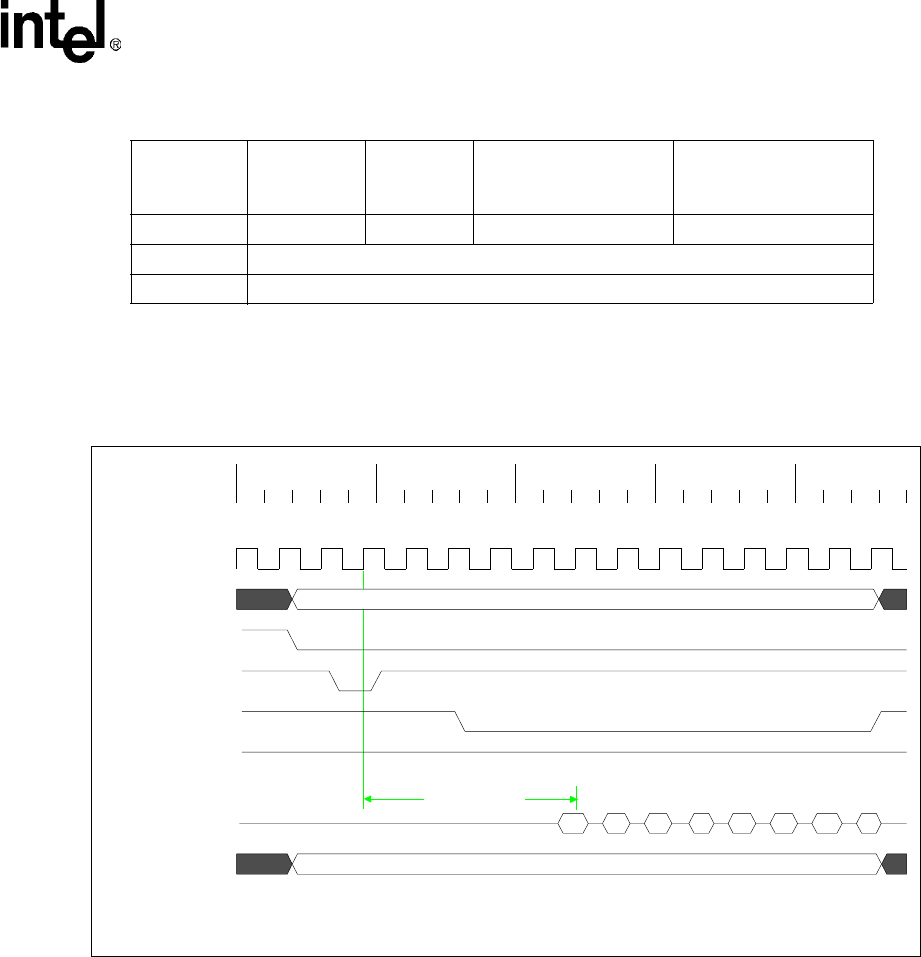

6.6.4.1 Non-SDRAM Timing Flash Read Timing Diagram

Figure 6-12 shows the burst-of-eight read timing diagram.

In Figure 6-13, the following timing parameters apply:

• nADV asserted time = 1 MEMCLK

• MA, nCS setup to nADV asserted = 1 MEMCLK

• nADV deasserted to nOE asserted = Code - 2 MEMCLKs

133 66 1 5 / 6 6 / 7

147 Not supported

166 Not supported

Table 6-18. Frequency Code Configuration Values Based on Clock Speed (Sheet 2 of 2)

MEMCLK

Frequency

SDCLK0

Frequency

MDREFR:

K0DB2

Valid

Frequency

Configurations

Corresponding

CAS Latencies

Figure 6-13. Burst-of-Eight Synchronous Flash Timing Diagram (non-divide-by-2 mode)

byte address

0000

SXCNFG[CL]

This diagram is for SXCNFG:CL = "100" (CAS Latency = 5) (Frequency Code Configuration = 4)

0ns 50ns 100ns 150ns 200ns

SDCLK[0]

MA[19:0]

nCS[0]

nADV(nSDCAS)

nOE

nWE

MD[31:0]

DQM[3:0]