14-12 Intel® PXA255 Processor Developer’s Manual

Inter-Integrated-Circuit Sound (I2S) Controller

14.6.4 Serial Audio Clock Divider Register (SADIV)

SADIV, shown in Table 14-8, is used for generating six different BITCLK frequencies and hence

six different sampling frequencies.

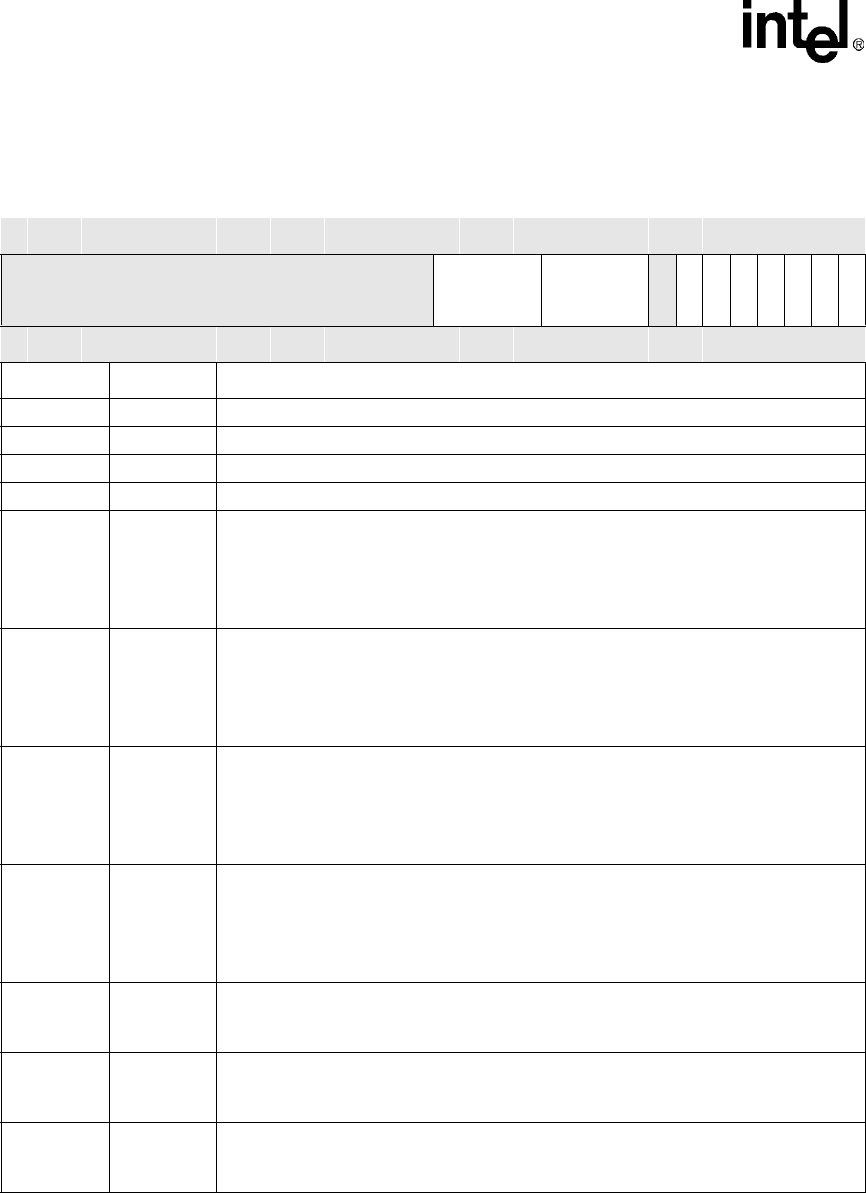

Table 14-7. SASR0 Bit Definitions

Physical Address

0x4040_000C

Serial Audio Controller I

2

S/MSB-

Justified Status Register

I

2

S Controller

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

reserved RFL TFL

reserved

ROR

TUR

RFS

TFS

BSY

RNE

TNF

Reset 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1

Bits Name Description

31:16 — reserved

15:12 RFL Receive FIFO Level: number of entries in Receive FIFO

11:8 TFL Transmit FIFO Level: number of entries in Transmit FIFO

7 — reserved

6ROR

Receive FIFO Overrun:

0 = Receive FIFO has not experienced an overrun

1 = I

2

S attempted data write to full Receive FIFO (Interruptible)

Can interrupt processor if bit6 of Serial Audio Interrupt Mask Register is set.

Cleared by setting bit 6 of Serial Audio Interrupt Clear Register.

5TUR

Transmit FIFO Under-run:

0 = Transmit FIFO has not experienced an under-run

1 = I

2

S attempted data read from an empty Transmit FIFO

Can interrupt processor if bit 5 of Serial Audio Interrupt Mask Register is set.

Cleared by setting bit 5 of Serial Audio Interrupt Clear Register.

4RFS

Receive FIFO Service Request:

0 = Receive FIFO level below RFL threshold, or I

2

S disabled

1 = Receive FIFO level is at or above RFL threshold.

Can interrupt processor if bit 4 of Serial Audio Interrupt Mask Register is set.

Cleared automatically when # of Receive FIFO entries < (RFTH + 1).

3 TFS

Transmit FIFO Service Request:

0 = Transmit FIFO level exceeds TFL threshold, or I

2

S disabled

1 = Transmit FIFO level is at or below TFL threshold

Can interrupt processor if bit 3 of Serial Audio Interrupt Mask Register is set.

Cleared automatically when # of Transmit FIFO entries >= (TFTH + 1).

2 BSY

I

2

S Busy:

0 = I

2

S is idle or disabled

1 = I

2

S currently transmitting or receiving a frame

1 RNE

Receive FIFO not empty:

0 = Receive FIFO is empty

1 = Receive FIFO is not empty

0TNF

Transmit FIFO not full:

0 = Transmit FIFO is full

1 = Transmit FIFO is not full