9-2 Intel® PXA255 Processor Developer’s Manual

I

2

C Bus Interface Unit

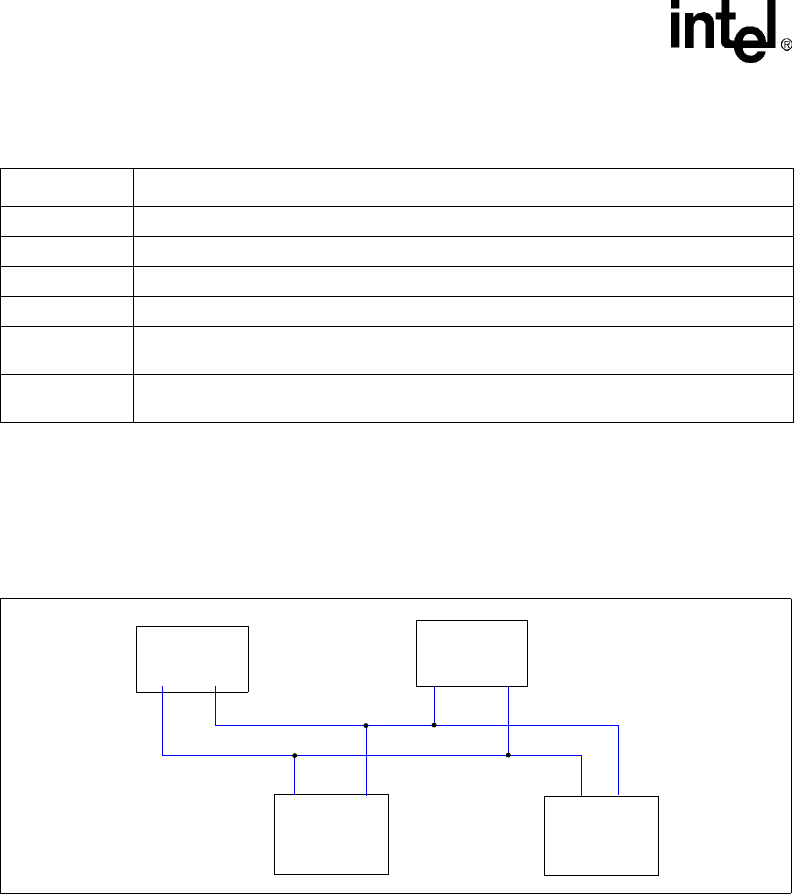

For example, when the processor I

2

C unit acts as a master on the bus, it addresses an EEPROM as

a slave to receive data (see Figure 9-1). When the I

2

C unit is addressing the EEPROM, it is a

master-transmitter and the EEPROM is a slave-receiver. When the I

2

C reads data, it is a master-

receiver and the EEPROM is a slave-transmitter. Whether it is a transmitter or receiver, the master

generates the clock, initiates the transaction, and terminates the transaction.

The I

2

C bus allows for a multi-master system, which means more than one device can initiate data

transfers at the same time. To support this feature, the I

2

C bus arbitration relies on the wired-AND

connection of all I

2

C interfaces to the I

2

C bus. Two masters can drive the bus simultaneously,

provided they drive identical data. If a master tries to drive SDA high while another master drives

SDA low, it loses the arbitration. The SCL line is a synchronized combination of clocks generated

by the masters using the wired-AND connection to the SCL line.

The I

2

C bus serial operation uses an open-drain wired-AND bus structure, which allows multiple

devices to drive the bus lines and to communicate status about events such as arbitration, wait

states, error conditions, etc. For example, when a master drives the clock (SCL) line during a data

transfer, it transfers a bit on every instance that the clock is high. When the slave is unable to accept

or drive data at the rate that the master is requesting, the slave can hold the clock line low between

the high states to insert a wait interval. The master’s clock can only be altered by another master

during arbitration or a slow slave peripheral that keeps the clock line low.

I

2

C transactions are either initiated by the processor as a master or received by the processor as a

slave. Both conditions may result in reads, writes, or both to the I

2

C bus.

Table 9-2.

I

2

C Bus Definitions

I

2

C Device Definition

Transmitter Sends data to the I

2

C bus.

Receiver Receives data from the I

2

C bus.

Master Initiates a transfer, generates the clock signal, and terminates the transactions.

Slave Device addressed by a master.

Multi-master

More than one master can attempt to control the bus at the same time without corrupting

the message.

Arbitration

Ensures that only one master controls the bus when more than one master simultaneously

tries to control the bus. This ensures that messages are not corrupted.

Figure 9-1. I

2

C Bus Configuration Example

Micro -

Controller

Gate

Array

EEPROM

SCL

SDA

Processor