5-8 Intel® PXA255 Processor Developer’s Manual

DMA Controller

5.1.4.3 Servicing an Interrupt

If software receives an interrupt caused by a successful descriptor fetch, i.e. DCSRx[STARTINTR]

= 0b1, then software must write a 1 to this bit to reset the corresponding interrupt. Software

normally accomplishes this by reading the DCSRx register, modifying the data value by setting the

DCSRx[STARTINTR]=0b1 and leaving the DCSRx[RUN] bit set, and then writing this modified

value back to the DCSRx. If the channel stops, DCSRx[RUN] = 0b0, before writing this value back

to the DCSRx, then software can inadvertently set the DCSRx[RUN] bit before properly

configuring other DMA registers. In order to avoid this problem, after writing the modified value

back to the DCSRx, software must read the DCSRx and check to see if DCSRx[RUN] and

DCSRx[STOPSTATE] are both set. If they are, then software must clear the DCSRx[RUN] bit and

re-initialize the DMA channel.

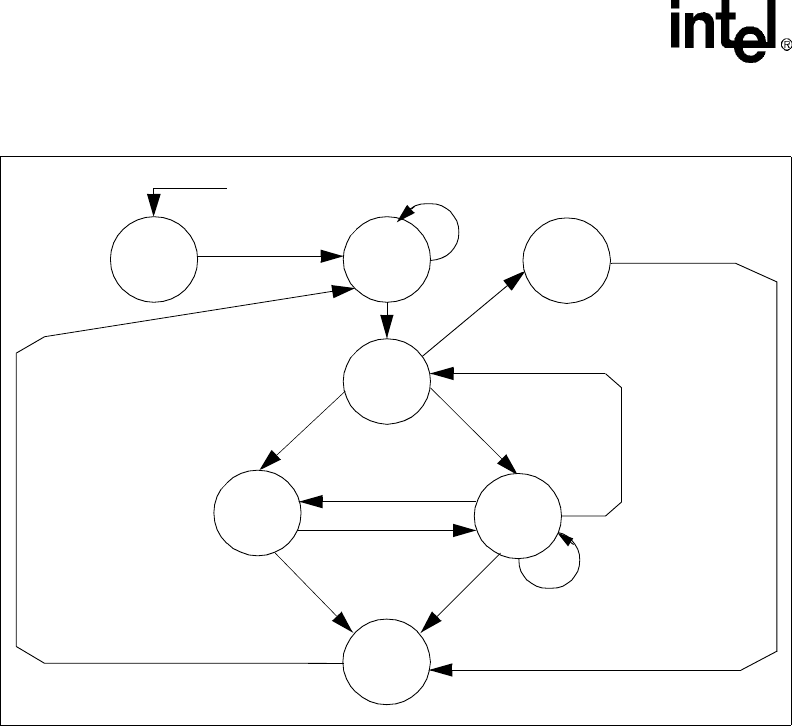

5.1.5 Channel States

A DMA channel can go through any of the following states:

• Uninitialized: Channel is in an uninitialized state after reset.

• Valid Descriptor, Not Running: Software has loaded a descriptor in the DDADR of the

channel, in the Descriptor Fetch Mode, or has programmed DSADR, DTADR and DCMD

values, in No-Descriptor Fetch Mode, but the corresponding run bit in the DCSR[RUN]

register is not set to a 1.

• Descriptor Fetch, Running: Fetching four words of descriptors from the memory.

Figure 5-4. Descriptor Fetch Mode Channel State

Uninitialized

Va l i d

Descriptor

RESET

(Hardware or Sleep)

not running

(running)

Wait

for

request

Transferring

Data

Stopped

descriptor

fetch

Error

Channel

RUN=1

DCMD[LENGTH] 0

& DCMD[FLOWSRC] = 0

& DCMD[FLOWTRG] = 0

DDADR[STOP] = 1

DDADR[STOP] = 1

DCMD[FLOWSRC] xor

DCMD[FLOWTRG] = 1

DCMD[FLOWSRC] &

DCMD[FLOWTRG] = 0

Request Asserted

DDADR[STOP] = 0

DCMD[FLOWSRC] xor

DCMD[FLOWTRG] = 1

RUN=0

≠