Intel® PXA255 Processor Developer’s Manual 6-61

Memory Controller

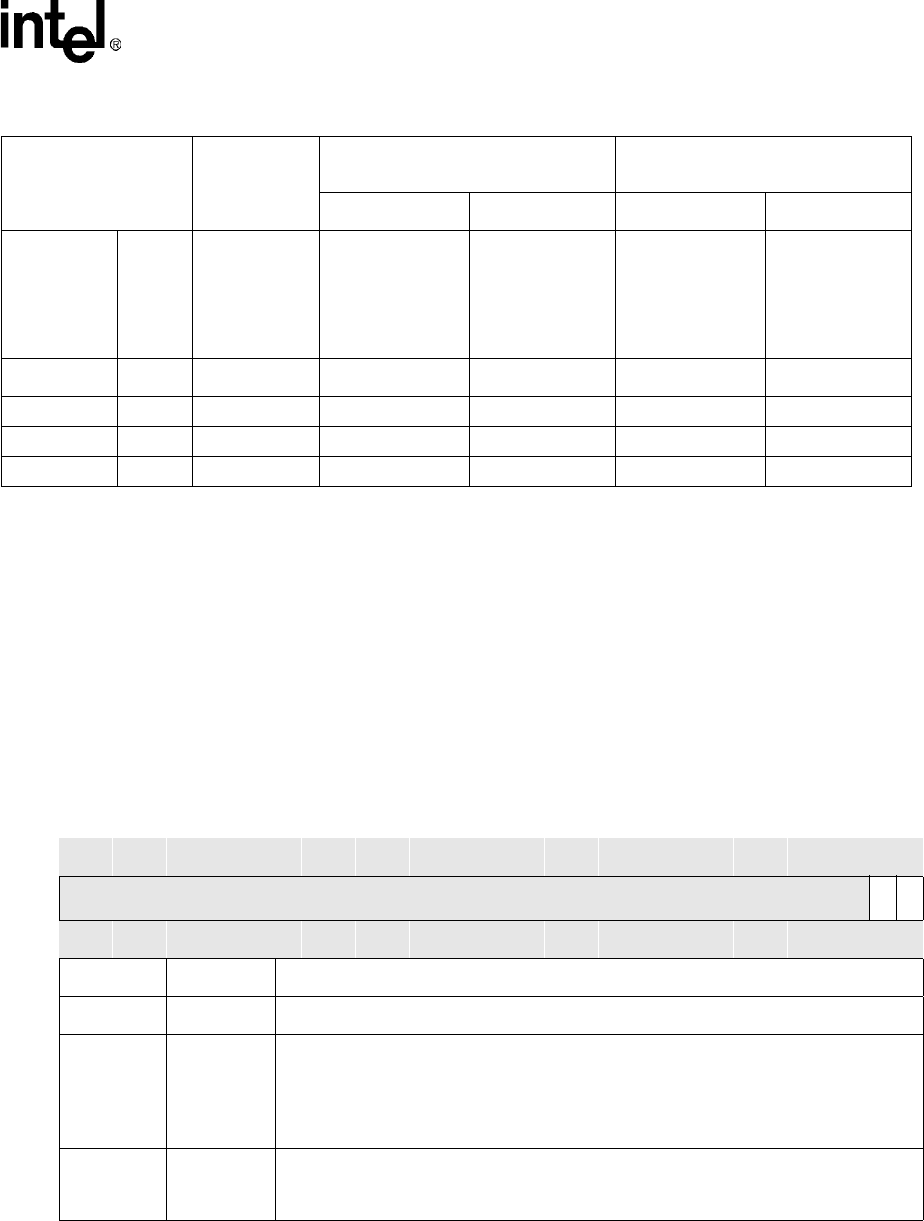

6.8.2 Expansion Memory Configuration Register (MECR)

To eliminate external hardware, the two bits in MECR, shown in Table 6-27, are used to signal the

memory controller when a card (16-Bit PC Card/Compact Flash) is inserted in the socket and the

number of cards supported in the system. The number-of-sockets bit is required because the

PSKTSEL pin is used as the nOE for the data transceivers in single socket mode. The card-is-there

bit is used to reduce external hardware by ignoring nIOIS16 and nPWAIT when there is no card

inserted in the socket.

This is a read/write register. Ignore reads from reserved bits. Write zeros to reserved bits.

11101 29 31 61 62 92 93

11110 30 32 63 64 95 96

11111 31 33 65 66 98 99

Table 6-26. Card Interface Command Assertion Code Table

MCMEMx_ASST

MCATTx_ASST

MCIOx_ASST

x_ASST_WAIT

x_ASST_HOLD

x_ASST_WAIT +

x_ASST_HOLD

(nPIOW asserted) (nPIOR asserted) (nPIOW asserted) (nPIOR asserted)

Programmed

Bit Value

Code

decimal

value

# MEMCLKs

(minimum)

to wait before

checking for

nPWAIT=’1’

# MEMCLKs

(minimum)

to assert

command

(nPIOW) after

nPWAIT=’1’

# MEMCLKs

(minimum)

to assert

command

(nPIOR) after

nPWAIT=’1’

# MEMCLKs

(minimum)

command

assertion time

# MEMCLKs

(minimum)

command

assertion time

(Code) (Code) (Code + 2) (2*Code + 3) (2*Code + 4) (3*Code + 5) (3*Code + 6)

Table 6-27. MECR Bit Definition

4800_0014 MECR Memory Controller

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

reserved

CIT

NOS

Reset 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Bits Name Description

31:2 — reserved

1CIT

Card-Is-There

0 – No card inserted

1 – Card inserted

Must be set by software when at least one card is present and must be cleared when all

cards are removed.

0NOS

Number-of-Sockets

0 – 1 Socket

1 – 2 Sockets