Intel® PXA255 Processor Developer’s Manual 16-5

Network SSP Serial Port

transmit data exist within the transmit FIFO. At other times, SSPSCLK holds in an inactive or idle

state as defined by the protocol.

16.4.3.1 TI Synchronous Serial Protocol* Details

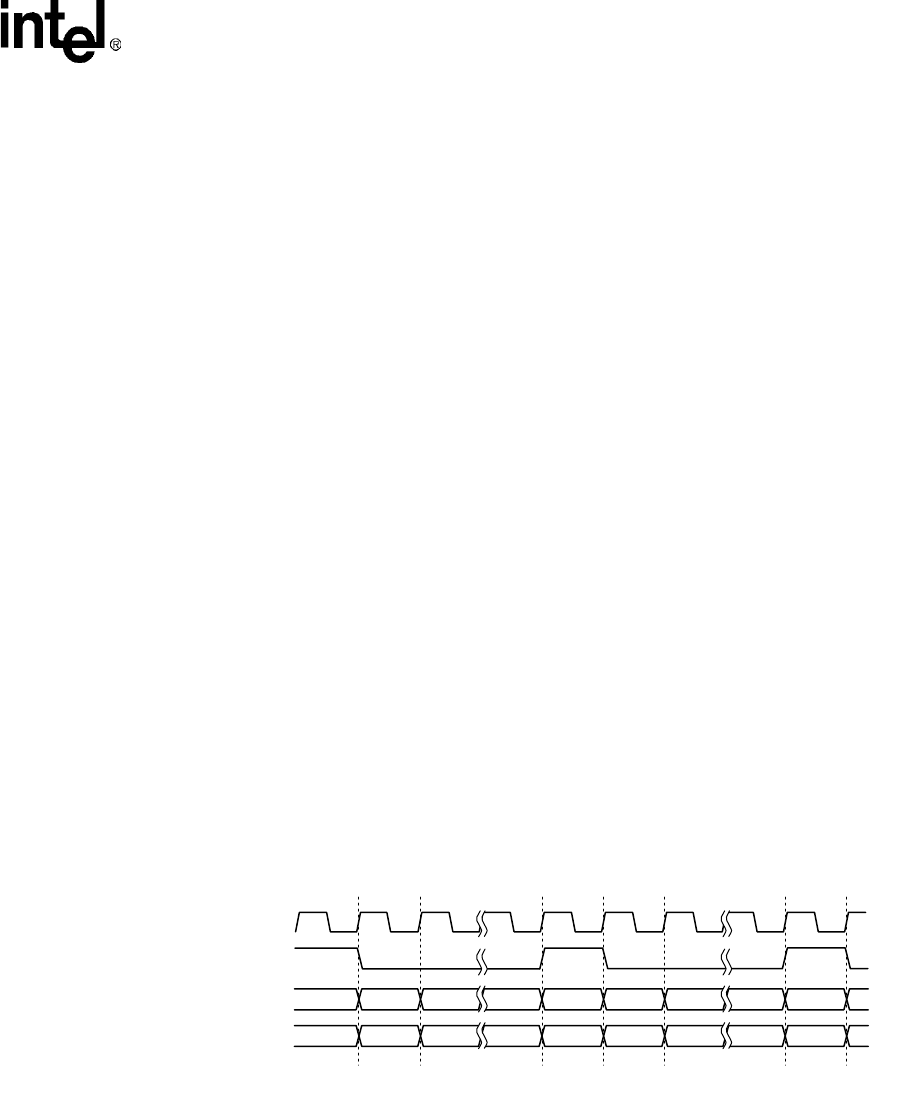

When outgoing data in the SSP controller is ready to transmit, SSPSFRM asserts for one clock

period. On the following clock, data to be transmitted is driven on SSPTXD one bit at a time, the

most significant bit first. For receive data, the peripheral similarly drives data on the SSPRXD pin.

The word length can be from four to 32-bits. All output transitions occur on the rising edge of

SSPSCLK while data sampling occurs on the falling edge. At the end of the transfer, the SSPTXD

signal either retains the value of the last bit sent (LSB) or clears depending on the serial form and

the value of the SSPSP[ETDS] (See Figure 16-1 through Figure 16-8). If the SSP is disabled or

reset, SSPTXD is forced low.

Figure 16-1 shows the TI Synchronous Serial Protocol for when back-to-back frames are

transmitted. Figure 16-2 shows the TI Synchronous Serial Protocol for a single transmitted frame.

Once the transmit FIFO contains data, SSPSFRM is pulsed high for one SSPSCLK period and the

value to be transmitted is transferred from the transmit FIFO to the transmit logic serial shift

register. On the next rising edge of SSPSCLK, the most significant bit of the four to 32-bit data

frame is shifted to the SSPTXD pin. Likewise, the MSB of the received data is shifted onto the

SSPRXD pin by the off-chip serial slave device. Both the SSP and the off-chip serial slave device

then latch each data bit into the serial shifter on the falling edge of each SSPSCLK. The received

data is transferred from the serial shifter to the receive FIFO on the first rising edge of SSPSCLK

after the last bit has been latched.

For back-to-back transfers, the start of one frame is the completion of the previous frame. The

MSB of one transfer immediately follows the LSB of the preceding with no “dead” time between

them. When the SSP is a master to the frame sync (SSPSFRM) and a slave to the clock

(SSPSCLK), at least three extra clocks are needed at the beginning and end of each block of

transfers to synchronize internal control signals (a block of transfers is a group of back-to-back

continuous transfers).

Figure 16-1. Texas Instruments Synchronous Serial Frame* Protocol (multiple transfers)

A9650-01

SSPSCLK

SSPSFRM

SSPTX

Bit[N] Bit[N-1] Bit[1] Bit[0] Bit[N] Bit[N-1] Bit[1]Bit[0]

SSPRX

Bit[N] Bit[N-1] Bit[1] Bit[0] Bit[N] Bit[N-1] Bit[1] Bit[0]

Bit[0]

Bit[0]