4-38 Intel® PXA255 Processor Developer’s Manual

System Integration Unit

4.5 Pulse Width Modulator

Use the Pulse Width Modulator (PWM) to generate as many as two signals to be output from the

processor. The signals are based on the 3.6864 MHz clock and must be a minimum of 2 clock

cycles wide. These signals are output from the processor by configuring the GPIOs.

4.5.1 Pulse Width Modulator Operation

The processor contains two pulse width modulators: PWM0 and PWM1. Each PWM operates

independently of the other, is controlled by its own set of registers. They provide a pulse width

modulated signal on an external pin. Since each PWM contains identical circuitry, a generic

PWMn, where n is 0 or 1, is described.

Each PWM contains:

• Two Pulse Width Modulator channels

• Enhanced Period control through 6-Bit Clock divider and 10-Bit Period counter

• 10-Bit Pulse control

A block diagram of one of the PWMs is shown in Figure 4-3.

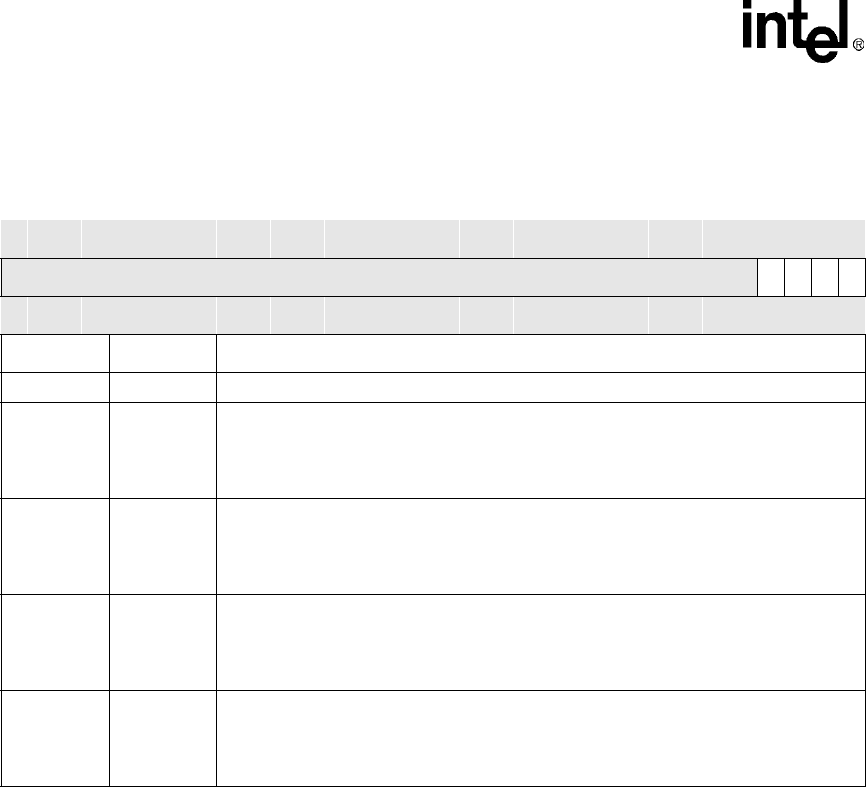

Table 4-45. OSSR Bit Definitions

Physical Address

0x40A0_0014

OS Timer Status Register (OSSR) System Integration Unit

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

reserved

M3

M2

M1

M0

Reset ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? 0 0 0 0

Bits Name Description

<31:4> — reserved

<3> M3

Match status channel 3.

If OIER[3] is set then:

0 – OSMR[3] has NOT matched the OS timer counter since last being cleared.

1 – OSMR[3] has matched the OS timer counter.

<2> M2

Match status channel 2.

If OIER[2] is set then:

0 – OSMR[2] has NOT matched the OS timer counter since last being cleared.

1 – OSMR[2] has matched the OS timer counter.

<1> M1

Match status channel 1.

If OIER[1] is set then:

0 – OSMR[1] has NOT matched the OS timer counter since last being cleared.

1 – OSMR[1] has matched the OS timer counter.

<0> M0

Match status channel 0.

If OIER[0] is set then:

0 – OSMR[0] has NOT matched the OS timer counter since last being cleared.

1 – OSMR[0] has matched the OS timer counter.